海狸 hvisor 技术手册

v0.3, 2025年10月22日

矽望泛在操作系统社区

https://www.syswonder.org

欢迎使用 hvisor!

hvisor是一款轻量级Type-1虚拟机监控器,使用Rust语言编写,其目标是在异构多核 SoC 平台上提供高效、安全、低开销的虚拟化能力。作为一个直接运行在裸机上的虚拟机监控器,Hvisor 具备快速启动、跨平台支持以及良好的内存安全特性,特别适合嵌入式、边缘计算、车载和工业控制等对性能与安全有严格要求的场景。Hvisor 的设计理念深受 Little.BIG 二元内核架构 启发,通过“轻量内核 + 完整内核”的方式,实现了硬件分区、虚拟化支持与多操作系统并行运行。

特点

- 跨平台支持:支持ARMv8,RISC-V,LoongArch, X86等多种架构。

- 轻量级:专注于核心虚拟化功能,避免了传统虚拟化解决方案中的不必要复杂性,适合资源受限的环境。

- 高效:直接运行在硬件上,无需通过操作系统层,提供接近原生的性能。

- 安全性:Rust语言以其内存安全性和并发编程模型著称,有助于减少内存泄漏、数据竞争等常见的系统级编程错误。

- 快速启动:设计简洁,启动时间短,适合需要快速部署虚拟化的场景。同时具备良好的可移植性,移植过程快捷、周期短。

主要功能

- 虚拟机管理:提供创建、启动、停止和删除虚拟机的基本管理功能。

- 资源分配与隔离:支持对CPU、内存和I/O设备的高效分配和管理,通过虚拟化技术确保不同虚拟机之间的隔离,提升系统安全性和稳定性。

使用场景

- 边缘计算:适合在边缘设备上运行,为IoT和边缘计算场景提供虚拟化支持。

- 开发和测试:开发者可以快速创建和销毁虚拟机环境,用于软件开发和测试。

- 安全研究:提供一个隔离环境,用于安全研究和恶意软件分析。

Little.BIG 架构理念

架构思想

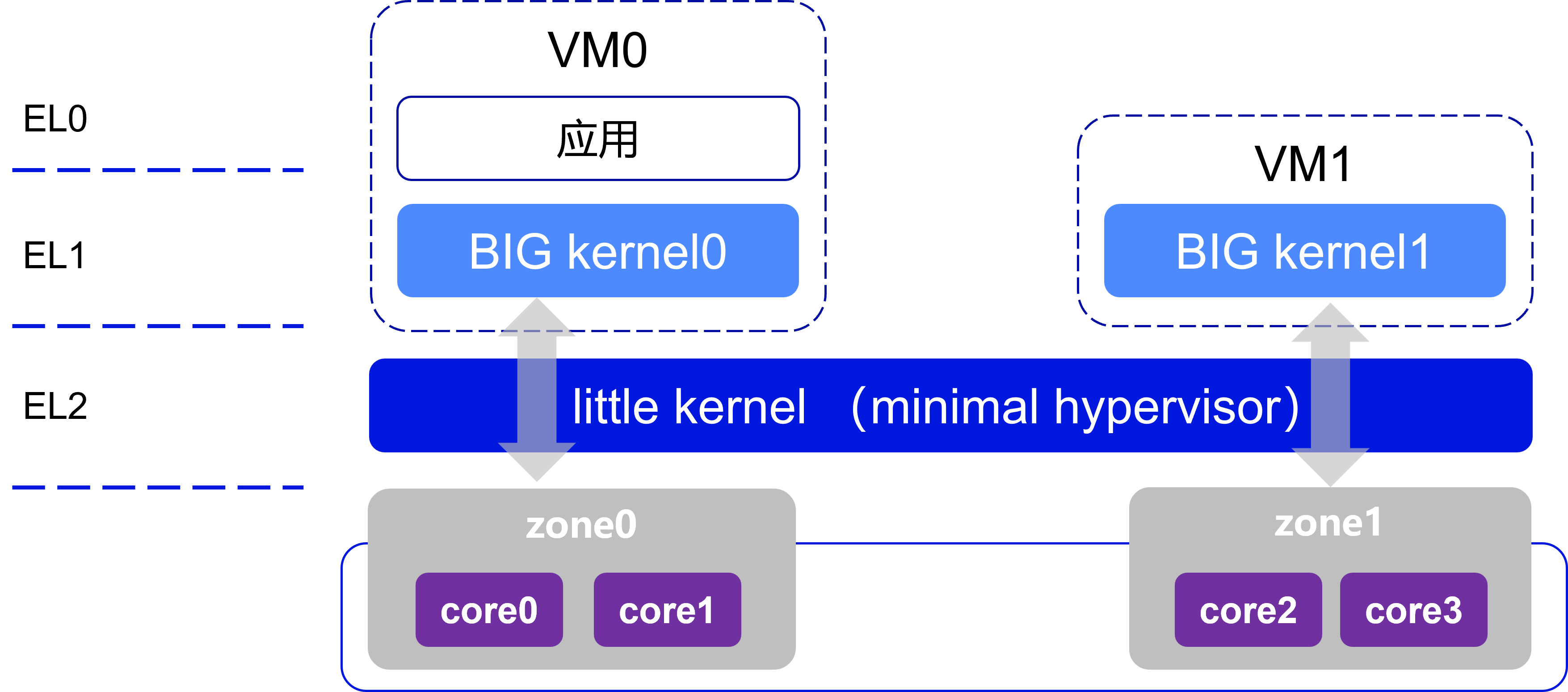

Little.BIG 二元内核架构将系统分为两类核心组件:

- Little Kernel(轻量内核):极简的 Type-1 Hypervisor,运行在裸机上,负责硬件分区与隔离,提供 CPU、内存、I/O 等的最小化虚拟化支持。

- BIG Kernel(大内核):运行在不同 zone 内的完整操作系统内核,如 Linux、RTOS、Unikernel 等,用于承载应用程序和系统服务。

Hvisor 整体架构

Hvisor 作为 Little.BIG 理念的实现,其整体架构分为三层:

-

BIG Kernel 层(Zone 层):在 Little.BIG 架构下,硬件被划分为多个 zone,每个 zone 独立运行自己的 OS 与应用:

zone0:运行 Linux,提供虚拟机管理、设备驱动、VirtIO 后端等。

zoneR:运行 RTOS,通过 xiUOS 库和 VirtIO 驱动支持实时应用。

zoneU:运行 Linux/RuxOS,支持单一应用优化。

-

Little Kernel 层(Hvisor):提供 Hypercall 接口供 BIG kernel 调用。

CPU 虚拟化:Trap 处理、PerCPU 静态分配。

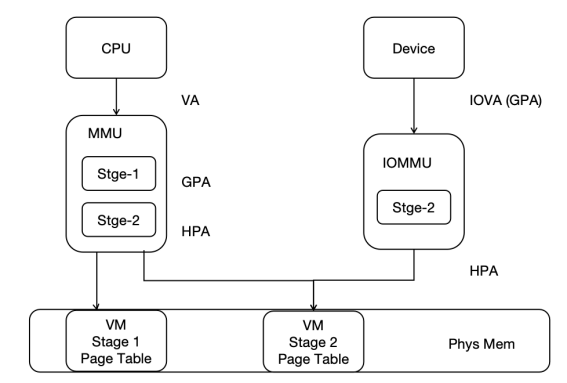

内存虚拟化:MMU 配置、Stage-2 页表映射。

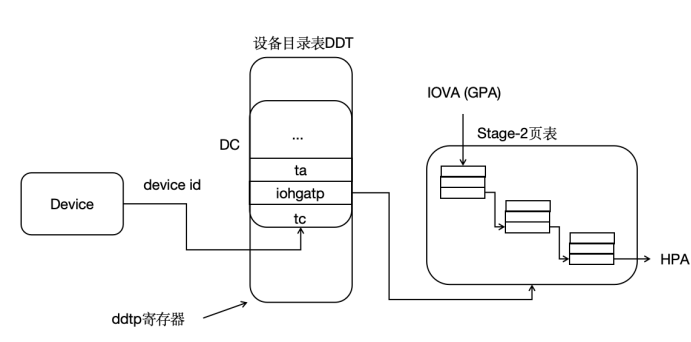

I/O 虚拟化:IOMMU、VirtIO 跳板、PCI 支持。

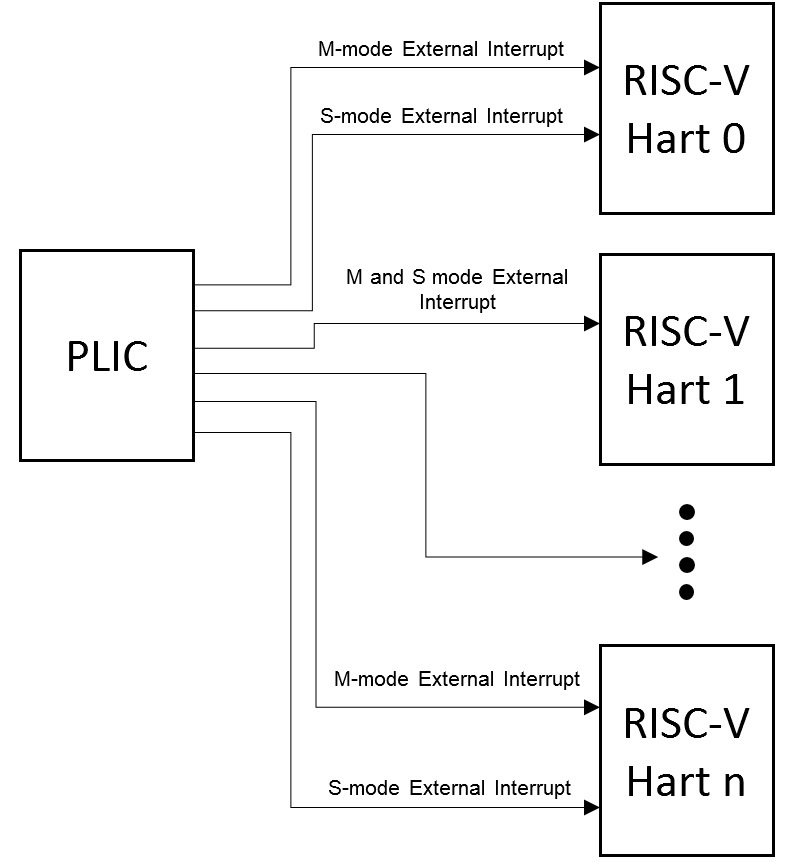

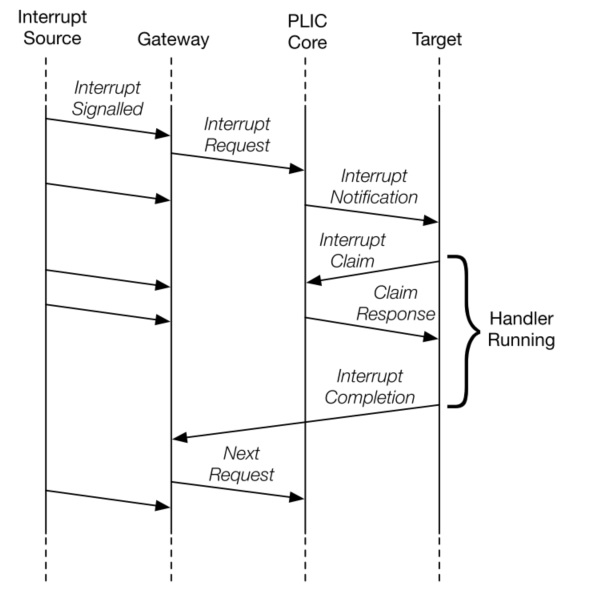

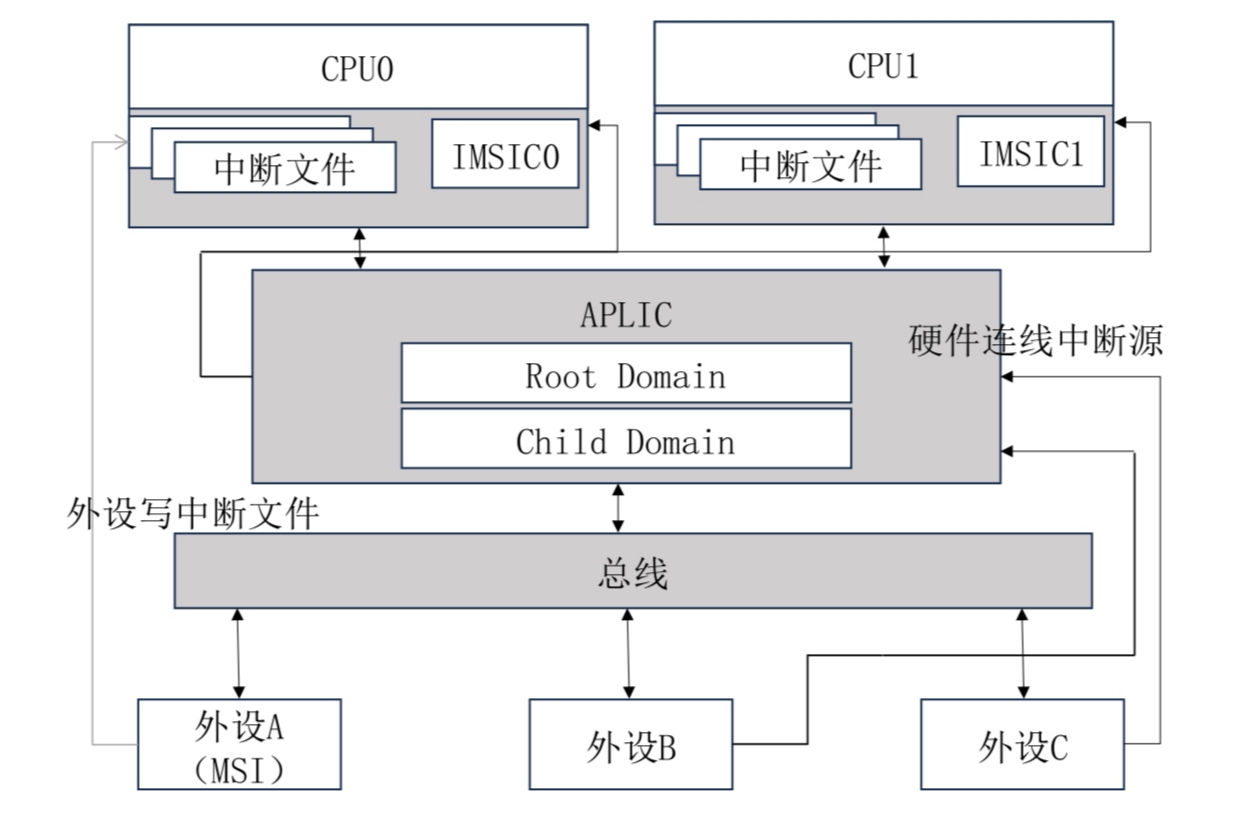

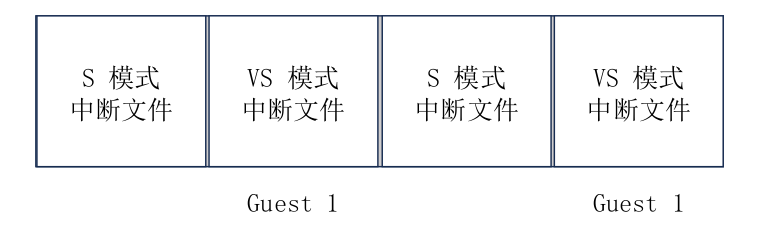

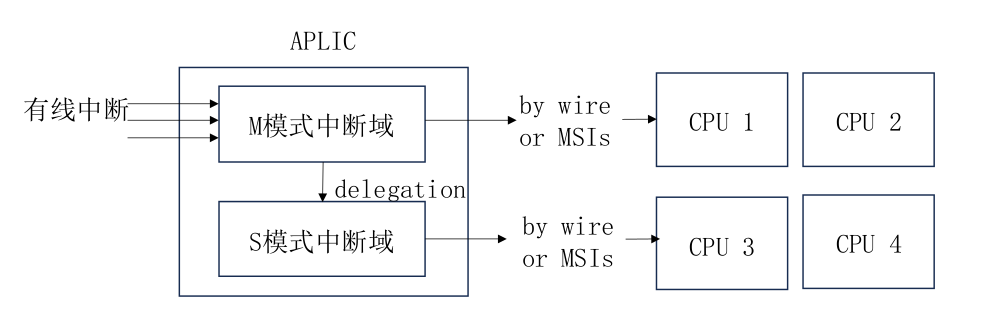

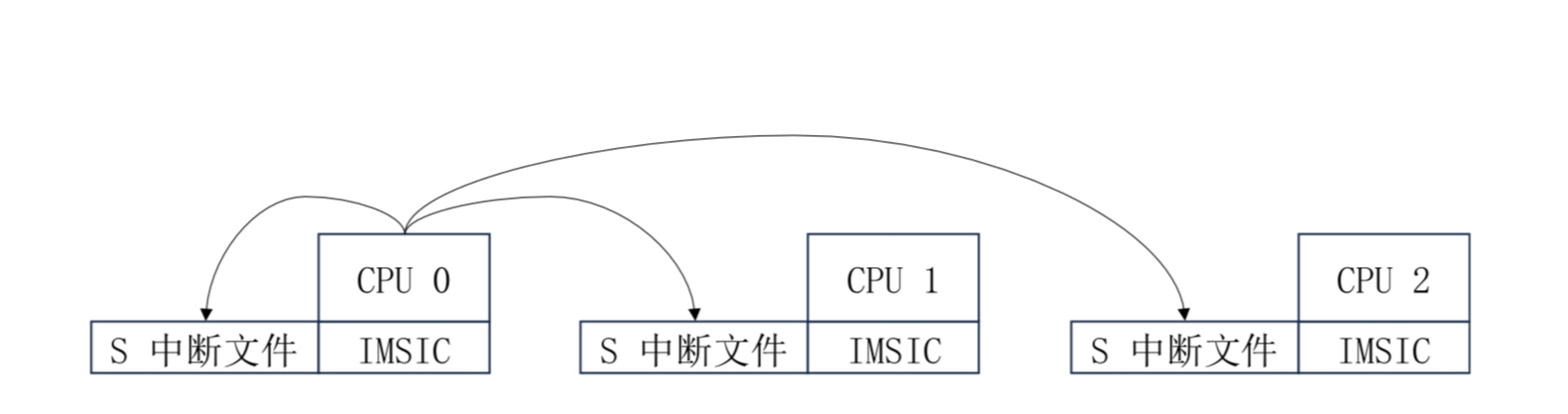

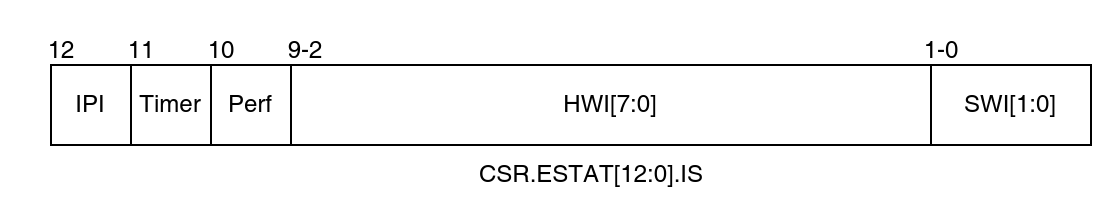

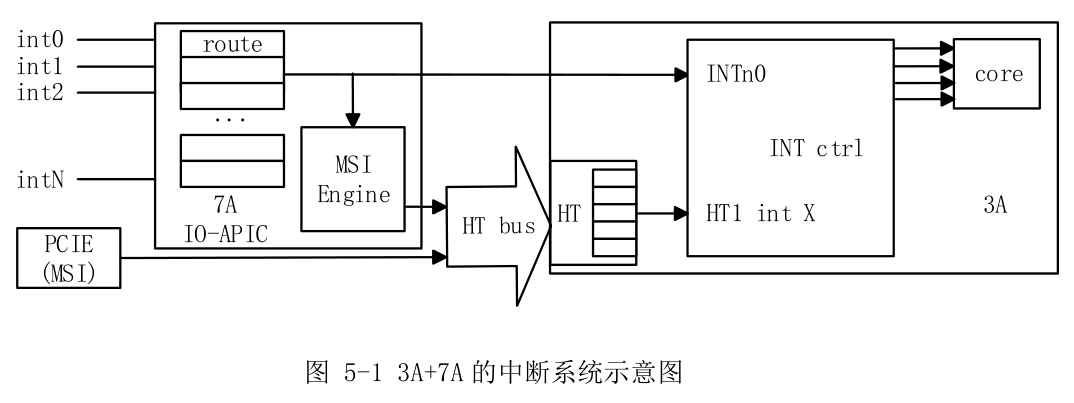

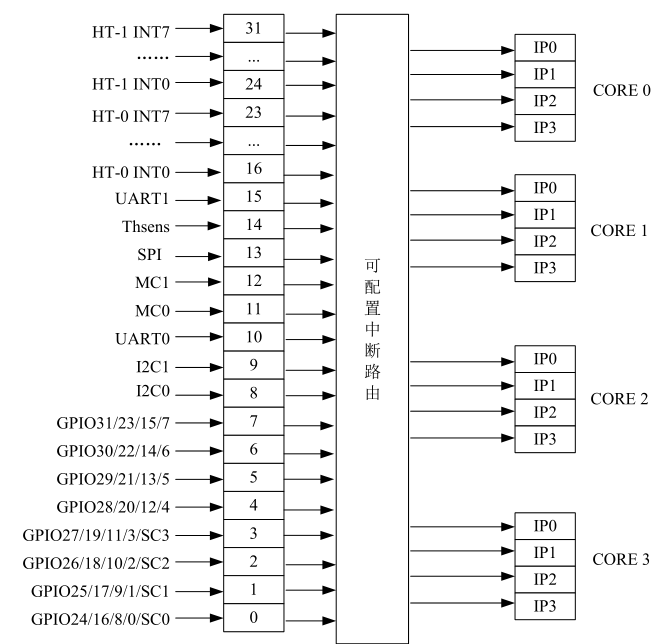

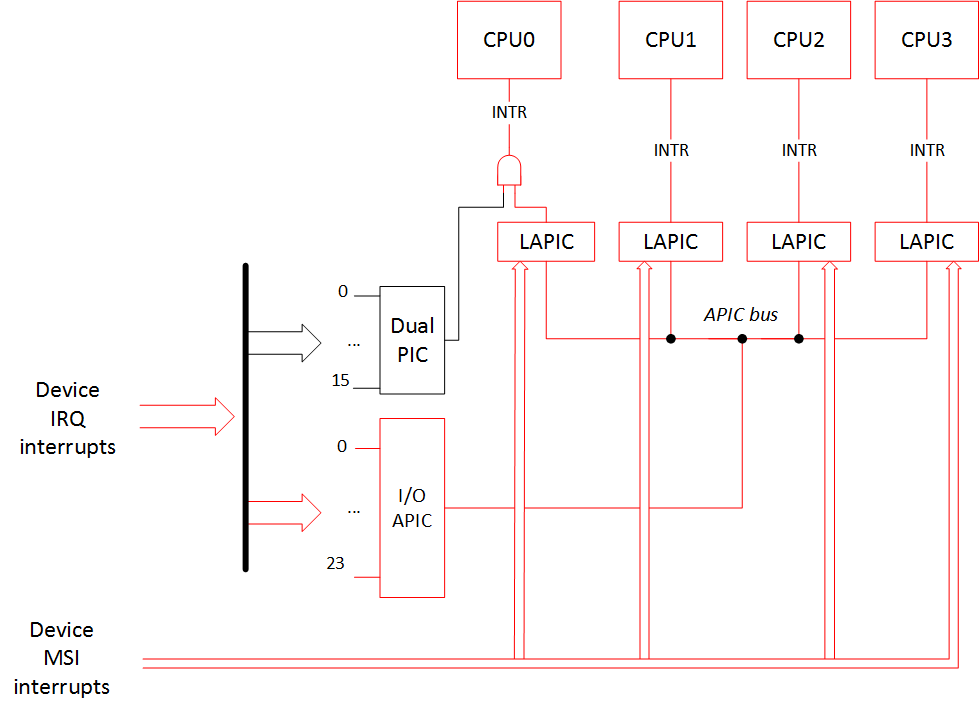

中断虚拟化:中断控制器模拟与中断注入。

-

硬件层:支持 DMA 与设备直通,提高性能。

异构 SoC 硬件,包括 CPU、DRAM、GPU、FPGA、网卡及 I/O 设备。

hvisor 支持的指令集和处理器

hvisor 目前支持 4 种指令集架构的处理器: ARMv8 aarch64, RISC-V64, LoongArch64, X86_64

hvisor 支持的硬件平台

ARMv8

- QEMU virt aarch64

- NXP i.MX8MP

- Xilinx Ultrascale+ MPSoC ZCU102

- Rockchip RK3588

- Rockchip RK3568

- Forlinx OK6254-C

- 飞腾派(腾珑E2000 )

RISC_V64

- QEMU virt riscv64

- Milk-V Megrez

- Sifive Hifive Premier P550

- FPGA 香山(昆明湖)on S2C Prodigy S7-19PS-2

loongarch64

- Loongson 3A5000+7A2000

- Loongson 3A6000

x86_64

- QEMU q35

- ASUS NUC 14 Essential

hvisor 硬件适配

设计原则

- 代码与板子配置分离:hvisor 本身的

src内部不出现任何platform_xxx相关的cfg。 - 平台独立性:引入之前的 hvisor-deploy 架构,在

platform目录下有序存放各个体系结构和板子的相关信息。 - 板卡目录索引:

- 统一采用

platform/$ARCH/$BOARD作为板卡专用目录。 - 每个板卡的唯一 BID (Board ID) 采用

ARCH/BOARD格式,例如aarch64/qemu-gicv3。

- 统一采用

- 编译简化:支持使用

BID=xxx/xxx直接指定板卡,同时兼容ARCH=xxx BOARD=xxx风格。 - 结构化配置:每个板卡目录包含如下文件:

linker.ld- 链接脚本platform.mk- QEMU 启动 Makefile 及hvisor.bin处理board.rs- 板卡定义 Rust 代码configs/- hvisor-tool 启动 zone 的 JSON 配置cargo/features- 板卡对应的具体cargo features,包括驱动、功能等config.template.toml-.cargo/config的模板,由每个板子自己维护

test/- (可选) QEMU 相关测试代码,包括单元测试、系统测试等image/- 启动文件目录,包含多个子目录:bootloader/- (可选) 用于 QEMU 本地运行和 unittest/systemtest 测试dts/- (可选) zone 0, 1, 2, … 的设备树源文件its/- (可选) 用于 U-Boot FIT image 生成(hvisor aarch64 zcu102)iso/- (可选) 用于 GRUB image 生成(hvisor x86_64)kernel/- (可选) 适用于目标平台的 kernel Imagevirtdisk/- (可选) 虚拟磁盘文件,如 rootfs 等font/- (可选) 在显示器上打印调试日志信息使用的字体

代码实现细节

自动生成 .cargo/config.toml

- 通过

tools/gen_cargo_config.sh生成,确保linker.ld配置动态更新。 config.template.toml采用__ARCH__、__BOARD__等占位符,由gen_cargo_config.sh替换,生成.cargo/config.toml。

build.rs 自动软链接 board.rs

build.rs负责将platform/$ARCH/$BOARD/board.rs软链接到src/platform/__board.rs。- 避免 Makefile 处理,每次构建仅在

env变量变更时触发,减少不必要的全量编译。

通过 Cargo features 选择驱动

- 避免

platform_xxx直接出现在src/,改为基于features进行配置。 cargo/features统一存储板卡驱动、功能等配置。

各板卡对应 features 一览

| BOARD ID | FEATURES |

|---|---|

aarch64/qemu-gicv3 | gicv3 pl011 iommu pci pt_layout_qemu |

aarch64/qemu-gicv2 | gicv2 pl011 iommu pci pt_layout_qemu |

aarch64/imx8mp | gicv3 imx_uart |

aarch64/zcu102 | gicv2 xuartps |

riscv64/qemu-plic | plic |

riscv64/qemu-aia | aia |

loongarch64/ls3a5000 | loongson_chip_7a2000 loongson_uart loongson_cpu_3a5000 |

loongarch64/ls3a6000 | loongson_chip_7a2000 loongson_uart loongson_cpu_3a6000 |

aarch64/rk3588 | gicv3 uart_16550 uart_addr_rk3588 pt_layout_rk |

aarch64/rk3568 | gicv3 uart_16550 uart_addr_rk3568 pt_layout_rk |

x86_64/qemu | pci uart16550a |

x86_64/nuc14mnk | pci uart16550a |

开发与编译指南

编译不同板卡

make ARCH=aarch64 BOARD=qemu-gicv3

make BID=aarch64/qemu-gicv3 # 使用 BID 简写

make BID=aarch64/imx8mp

make BID=loongarch64/ls3a5000

make BID=x86_64/qemu

适配新板卡

- 确定

features:对照已有features归类,添加所需驱动和配置。 - 创建

platform/$ARCH/$BOARD目录:- 添加

linker.ld,board.rs,features等文件。

- 添加

- 编译测试:

make BID=xxx/new_board

features 设计原则

- 最小化层次:

- 例如

cpu-a72而不是board_xxx,以便多个板卡复用。

- 例如

- 明确驱动/功能分类:

irqchip(gicv3,plic, ...)uart(pl011,imx_uart, ...)iommu,pci,pt_layout_xxx, ...

在 QEMU 上运行 hvisor

一、安装交叉编译器 aarch64-none-linux-gnu-10.3

网址:https://developer.arm.com/downloads/-/gnu-a。

工具选择:AArch64 GNU/Linux target(aarch64-none-linux-gnu)。

# 下载交叉编译器并解压

wget https://armkeil.blob.core.windows.net/developer/Files/downloads/gnu-a/10.3-2021.07/binrel/gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-gnu.tar.xz

tar -xvf gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-gnu.tar.xz

# 查看解压后的可执行文件

ls gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-gnu/bin/

安装完成,记住路径,例如 /home/tools/gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-gnu/bin/aarch64-none-linux-gnu-,之后都会使用这个路径。

二、编译安装 QEMU 9.0.1

注意,QEMU 需要从 7.2.12 换成 9.0.1,以正常使用 PCI 虚拟化。

# 安装编译所需的依赖包

sudo apt install autoconf automake autotools-dev curl libmpc-dev libmpfr-dev libgmp-dev \

gawk build-essential bison flex texinfo gperf libtool patchutils bc \

zlib1g-dev libexpat-dev pkg-config libglib2.0-dev libpixman-1-dev libsdl2-dev \

git tmux python3 python3-pip ninja-build

# 下载源码并解压

wget https://download.qemu.org/qemu-9.0.1.tar.xz

tar -xvf qemu-9.0.1.tar.xz

cd qemu-9.0.1

# 生成配置并编译

./configure --enable-kvm --enable-slirp --enable-debug --target-list=aarch64-softmmu,x86_64-softmmu

make -j$(nproc)

之后编辑 ~/.bashrc 文件,在文件的末尾加入几行:

# 请注意,qemu-9.0.1 的父目录可以随着你的实际安装位置灵活调整。另外需要把其放在 $PATH 变量开头。

export PATH="/path/to/qemu-9.0.1/build:$PATH"

随后即可在当前终端 source ~/.bashrc 更新系统路径,或者直接重启一个新的终端。此时可以确认 qemu 版本,如果显示为 qemu-9.0.1,则表示安装成功:

qemu-system-aarch64 --version # 查看版本

注意,上述依赖包可能不全,例如:

- 出现

ERROR: pkg-config binary 'pkg-config' not found时,可以安装pkg-config包;- 出现

ERROR: glib-2.48 gthread-2.0 is required to compile QEMU时,可以安装libglib2.0-dev包;- 出现

ERROR: pixman >= 0.21.8 not present时,可以安装libpixman-1-dev包。

若生成设置文件时遇到报错

ERROR: Dependency "slirp" not found, tried pkgconfig:下载 https://gitlab.freedesktop.org/slirp/libslirp 包,并按 README 安装即可。

三、编译 Linux Kernel 5.4

注意,在最后编译 Linux Kernel 前,需修改默认生成的配置文件。需要启用 CONFIG_BLK_DEV_RAM,以启用 RAM 块设备支持;需要启用 CONFIG_IPV6 和 CONFIG_BRIDGE,以支持在 root linux 中创建网桥和 tap 设备。

交叉编译 Linux Kernel 5.4 生成 root linux 的镜像,用于在 hvisor 中启动 root linux。

# CROSS_COMPILE 路径需要根据第一步安装交叉编译器的路径进行更改

CROSS_COMPILE_PATH="<路径>/bin"

# 下载 linux 5.4 源码

git clone https://github.com/torvalds/linux -b v5.4 --depth=1

cd linux

git checkout v5.4

# 生成默认的编译配置

CROSS_COMPILE_PREFIX=${CROSS_COMPILE_PATH}/aarch64-none-linux-gnu-

make ARCH=arm64 CROSS_COMPILE=${CROSS_COMPILE_PREFIX} defconfig

# 启用 CONFIG_BLK_DEV_RAM,以启用 RAM 块设备支持

./scripts/config --enable CONFIG_BLK_DEV_RAM

# 启用 CONFIG_IPV6 和 CONFIG_BRIDGE,以支持在 root linux 中创建网桥和 tap 设备

./scripts/config --enable CONFIG_IPV6

./scripts/config --enable CONFIG_BRIDGE

# 编译

make ARCH=arm64 CROSS_COMPILE=${CROSS_COMPILE_PREFIX} Image -j$(nproc)

如果编译 linux 时报错:

/usr/bin/ld: scripts/dtc/dtc-parser.tab.o:(.bss+0x20): multiple definition of `yylloc'; scripts/dtc/dtc-lexer.lex.o:(.bss+0x0): first defined here则修改 linux 文件夹下

scripts/dtc/dtc-lexer.lex.c,在YYLTYPE yylloc;前增加extern。再次编译,发现会报错openssl/bio.h: No such file or directory,此时执行sudo apt install libssl-dev。

编译过程中会出现:

RAM block device support (BLK_DEV_RAM) [Y/n/m/?] y Default number of RAM disks (BLK_DEV_RAM_COUNT) [16] (NEW) Default RAM disk size (kbytes) (BLK_DEV_RAM_SIZE) [4096] (NEW)即配置具体参数,直接回车采用默认值即可。

编译完毕,内核文件位于 arch/arm64/boot/Image。记住整个 linux 文件夹所在的路径,例如 /home/korwylee/lgw/hypervisor/linux,在第七步我们还会用到这个路径。

四、基于 Ubuntu 22.04 arm64 base 构建文件系统

本部分的内容可以省略,直接下载该现成的磁盘镜像使用即可。https://blog.syswonder.org/#/2024/20240415_Virtio_devices_tutorial。

我们使用 Ubuntu 22.04 来构建根文件系统。

Ubuntu 20.04 也可以,但是运行时会报 glibc 版本低的错误,可参考 ARM64-qemu-jailhouse 评论区中的解决办法。

# QEMU 路径,需要根据第二步安装时的路径进行更改

QEMU_PATH="<路径>/build/qemu-system-aarch64"

# 下载 ubuntu base

wget http://cdimage.ubuntu.com/ubuntu-base/releases/22.04/release/ubuntu-base-22.04.5-base-arm64.tar.gz

# 创建 rootfs,用于挂载后续的 rootfs1.img

mkdir -p rootfs

# 创建一个 1 GiB 大小的 rootfs1.img,可以通过修改 count 修改 img 大小

dd if=/dev/zero of=rootfs1.img bs=1M count=1024 oflag=direct

# 格式化为 ext4 文件系统

mkfs.ext4 rootfs1.img

# 挂载 rootfs1.img

sudo mount -t ext4 rootfs1.img rootfs/

# 将 ubuntu.tar.gz 的内容解压到 rootfs

sudo tar -xzf ubuntu-base-22.04.5-base-arm64.tar.gz -C rootfs/

# 让 rootfs 绑定和获取物理机的一些信息和硬件

sudo cp "${QEMU_PATH}" rootfs/usr/bin/

sudo cp /etc/resolv.conf rootfs/etc/resolv.conf

sudo mount -t proc /proc rootfs/proc

sudo mount -t sysfs /sys rootfs/sys

sudo mount -o bind /dev rootfs/dev

sudo mount -o bind /dev/pts rootfs/dev/pts

# 将文件系统切换到 rootfs

sudo chroot rootfs # 执行该指令可能会报错,请参考下面的解决办法

# 在 rootfs 中安装必要的软件包

apt-get update

apt-get install git sudo vim bash-completion \

kmod net-tools iputils-ping resolvconf ntpdate screen

apt-get clean

# 以下由 # 圈住的内容可做可不做

###################

adduser arm64

adduser arm64 sudo

echo "kernel-5_4" > /etc/hostname

echo "127.0.0.1 localhost" > /etc/hosts

echo "127.0.0.1 kernel-5_4" >> /etc/hosts

dpkg-reconfigure resolvconf

dpkg-reconfigure tzdata

###################

# 退出 rootfs

exit

# 卸载 rootfs

sudo umount rootfs/proc

sudo umount rootfs/sys

sudo umount rootfs/dev/pts

sudo umount rootfs/dev

sudo umount rootfs

此时可以顺便创建后续要用到的

rootfs2.img,其大小应适当减少,以便放入rootfs1.img中。# QEMU 路径,需要根据第二步安装时的路径进行更改 QEMU_PATH="<路径>/build/qemu-system-aarch64" # 创建 rootfs2.img,其大小适当减少到 256 MiB dd if=/dev/zero of=rootfs2.img bs=1M count=256 oflag=direct mkfs.ext4 rootfs2.img sudo mount -t ext4 rootfs2.img rootfs/ sudo tar -xzf ubuntu-base-22.04.5-base-arm64.tar.gz -C rootfs/ sudo cp "${QEMU_PATH}" rootfs/usr/bin/ sudo cp /etc/resolv.conf rootfs/etc/resolv.conf sudo mount -t proc /proc rootfs/proc sudo mount -t sysfs /sys rootfs/sys sudo mount -o bind /dev rootfs/dev sudo mount -o bind /dev/pts rootfs/dev/pts sudo umount rootfs/proc sudo umount rootfs/sys sudo umount rootfs/dev/pts sudo umount rootfs/dev sudo umount rootfs

最后卸载挂载,完成根文件系统的制作。

执行

sudo chroot rootfs时,如果报错chroot: failed to run command '/bin/bash': Exec format error,可以执行指令:sudo apt-get install qemu-user-static sudo update-binfmts --enable qemu-aarch64

五、Rust 环境配置

请参考 Rust 语言圣经。

六、编译和运行 hvisor

首先将 hvisor 代码仓库 拉到本地,并切换到 dev 分支。

运行前需要准备好 hvisor 的平台配置文件,具体准备工作包括根文件系统、Linux 内核镜像以及编译对应的设备树文件,现 hvisor 各平台配置文件在仓库的 platform/<架构>/<平台名>/ 路径下,例如本教程将采用的配置文件位于 platform/aarch64/qemu-gicv3/ 路径下。

# 复制根文件系统 rootfs1.ext4

ROOTFS1_PATH="<路径>/rootfs1.img"

mkdir -p platform/aarch64/qemu-gicv3/image/virtdisk

cp "${ROOTFS1_PATH}" platform/aarch64/qemu-gicv3/image/virtdisk/rootfs1.ext4

# 复制 Linux 内核镜像

KERNEL_PATH="<路径>/Image"

mkdir -p platform/aarch64/qemu-gicv3/image/kernel

cp "${KERNEL_PATH}" platform/aarch64/qemu-gicv3/image/kernel/Image

# 编译设备树

make BID=aarch64/qemu-gicv3 dtb

其实建议采用硬链接的方式,以便减轻磁盘空间的占用和方便根文件系统修改时同步。

之后在 hvisor 目录下,执行相应命令即可启动 hvisor。

make BID=aarch64/qemu-gicv3 LOG=info run

执行后会进入 uboot 启动界面,该界面下执行:

bootm 0x40400000 - 0x40000000

该启动命令会从物理地址 0x40400000 启动 hvisor,0x40000000 本质上已无用,但因历史原因仍然保留。hvisor 启动时,会自动启动 root linux(用于管理的 Linux),并进入 root linux 的 shell 界面,root linux 即为 zone0,承担管理工作。

提示缺少

dtc时,可以执行指令:sudo apt install device-tree-compiler

七、使用 hvisor-tool 启动 zone1-linux

首先完成最新版本的 hvisor-tool 的编译。具体请参考 hvisor-tool 的 README。

# Linux 源代码路径,需要根据第三步安装时的路径进行更改

LINUX_PATH="<路径>/linux"

git clone https://github.com/syswonder/hvisor-tool.git

cd hvisor-tool

make all ARCH=arm64 LOG=LOG_INFO KDIR="${LINUX_PATH}"

请务必保证 hvisor 中的 root linux 镜像是由编译 hvisor-tool 时参数选项中的 Linux 源代码目录编译产生。

请务必保证 hvisor-tool 编译时采用的 linux header 版本与 root linux 的 linux header 版本一致,否则 hvisor-tool 的 driver 可能会无法加载。 可以通过使用与第三步中的 root linux 相同的交叉编译工具链进行编译,即使用第一步的交叉编译器路径进行配置。

编译完成后,需要将 hvisor-tool 的可执行文件 tools/hvisor 和内核模块 driver/hvisor.ko 复制到 root linux 的根文件系统中启动 zone1 linux 的目录,例如 /root,再同时将 zone1 的根文件系统、内核镜像、以及编译后的设备树放在同一目录。

具体的文件名需要与 hvisor-tool 配置文件(来自 hvisor 的 platform/aarch64/qemu-gicv3/configs/zone1-linux-virtio.json 和 platform/aarch64/qemu-gicv3/configs/zone1-linux.json)的内容保持一致。

按照 hvisor 提供的配置文件,可执行命令如下。

# 回到创建的 root linux 根文件系统时的目录

LINUX_PATH="<路径>/linux"

HVISOR_PATH="<路径>/hvisor"

HVISOR_TOOL_PATH="<路径>/hvisor-tool"

# 挂载

sudo mount -t ext4 rootfs1.img rootfs/

# 复制 hvisor-tool 的 driver/hvisor.ko 和 tools/hvisor

sudo cp "${HVISOR_TOOL_PATH}/driver/hvisor.ko" rootfs/root/

sudo cp "${HVISOR_TOOL_PATH}/tools/hvisor" rootfs/root/

# 复制 hvisor-tool 的配置文件到 root 路径下

sudo cp "${HVISOR_PATH}/platform/aarch64/qemu-gicv3/configs/zone1-linux-virtio.json" \

rootfs/root/zone1-linux-virtio.json

sudo cp "${HVISOR_PATH}/platform/aarch64/qemu-gicv3/configs/zone1-linux.json" \

rootfs/root/zone1-linux.json

# 复制 zone1 linux 的根文件系统、内核镜像、以及编译后的设备树

sudo cp rootfs2.img \

rootfs/root/rootfs2.ext4

sudo cp "${LINUX_PATH}/arch/arm64/boot/Image" \

rootfs/root/Image

sudo cp "${HVISOR_PATH}/platform/aarch64/qemu-gicv3/image/dts/zone1-linux.dtb" \

rootfs/root/zone1-linux.dtb

# 卸载

sudo umount rootfs

# 如果之前是复制的 rootfs1.img,则还需重新复制一份,命令如下

# 切换到 hvisor 目录

# ROOTFS1_PATH="<路径>/rootfs1.img"

# mkdir -p platform/aarch64/qemu-gicv3/image/virtdisk

# cp "${ROOTFS1_PATH}" platform/aarch64/qemu-gicv3/image/virtdisk/rootfs1.ext4

如果遇到

rootfs1.ext4容量不够,则可以参考 img 扩容 为rootfs1.ext4扩容。

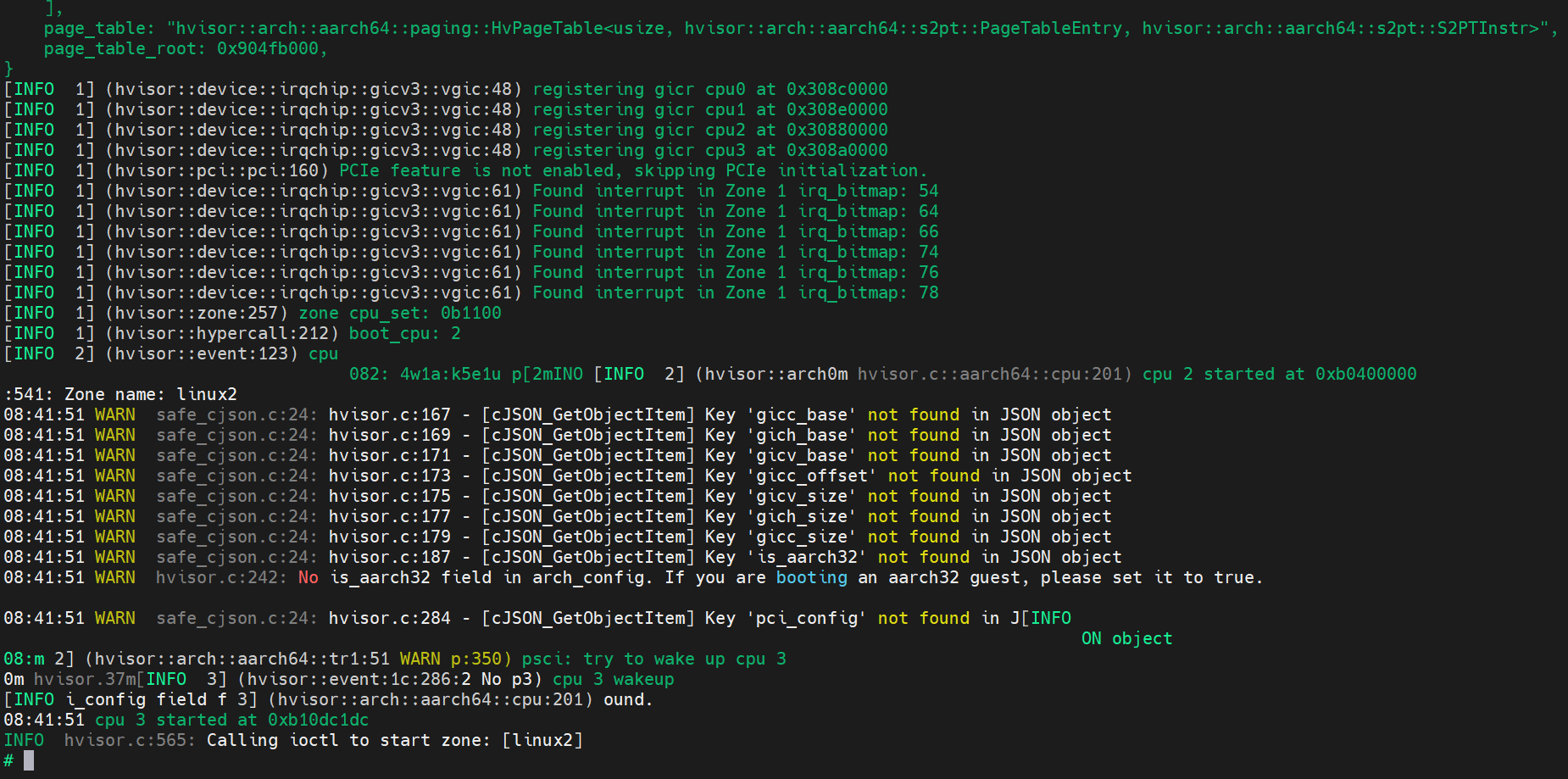

之后在 QEMU 上即可通过 root linux 启动 zone1-linux。具体命令如下。

# 启动 QEMU

make BID=aarch64/qemu-gicv3 LOG=info run

# 启动 root linux

bootm 0x40400000 - 0x40000000

cd root

insmod hvisor.ko

mount -t proc proc /proc

mount -t sysfs sysfs /sys

mkdir -p /dev/pts

mount -t devpts devpts /dev/pts

rm nohup.out

# 启动 zone1-linux 的 virtio

nohup ./hvisor virtio start zone1-linux-virtio.json &

# 启动 zone1-linux

./hvisor zone start zone1-linux.json && \

cat nohup.out | grep "char device" && \

script /dev/null

启动 zone1-linux 的详细步骤参看 hvisor-tool 的 README 以及 启动示例。

如果显示 virtio 出现 WARNING 或者 ERROR,可以查看

nohup.out查看详细信息,或者使用dmesg命令查看内核日志。

在 Qemu 上运行 hvisor

我们建议在 Ubuntu 上进行实践,以下示例均基于 Ubuntu 发行版。

若你的操作系统为 Windows,你可以使用 WSL 或者 VMware/VirtualBox 虚拟机。

一、安装 Qemu

若你已经拥有合适的 Qemu 可以使用,你可以跳过这一步。

我们建议使用源码编译的 Qemu,这样可以更加灵活地进行版本控制以及修改 Qemu 源码等等。

这里以 Qemu v9.0.2 为例,你也可以选择最新的版本:

# 安装依赖

sudo apt-get install git libglib2.0-dev libfdt-dev libpixman-1-dev zlib1g-dev ninja-build

# 获取 Qemu 源码

wget https://download.qemu.org/qemu-9.0.2.tar.xz

# 解压

tar xvJf qemu-9.0.2.tar.xz

# 进入源码目录

cd qemu-9.0.2

# 配置 riscv target

./configure --target-list=riscv64-softmmu,riscv64-linux-user

# 编译 qemu

make -j$(nproc)

# 测试是否安装成功

./build/qemu-system-riscv64 --version

你可以选择将它安装到环境变量,这样你可以使用 qemu-system-riscv64,而无需显式标明路径。

一种常见的方式是将其安装到 /opt/riscv, 并配置环境变量指向它。

二、安装 riscv 交叉编译器

我们需要用 riscv 交叉编译器来将 Linux 与 OpenSBI 编译成二进制文件,这里选择 https://github.com/riscv-collab/riscv-gnu-toolchain 。

建议从 Github Release 处下载编译好的交叉编译器,这里推荐下载 riscv64-glibc-ubuntu-xxxx-gcc、riscv64-elf-ubuntu-xxxx-gcc 两个压缩包。

一种常见的方式是将其安装到 /opt/riscv, 并配置环境变量指向它。

注意:这里不推荐使用源码编译,因为你可能会遇到各种各样的问题。

三、编译 Linux

如果你要运行 qemu-aia platform,请选择 linux v6.10 及以上版本,低版本的 linux 中不含 aia 的驱动,会导致 linux 无法正常工作。

这里以 linux v6.10 为例:

git clone https://github.com/torvalds/linux -b v6.10 --depth=1

cd linux

git checkout v6.10

make ARCH=riscv CROSS_COMPILE=riscv64-unknown-linux-gnu- defconfig

make ARCH=riscv CROSS_COMPILE=riscv64-unknown-linux-gnu- -j$(nproc)

四、制作 ubuntu 根文件系统

ubuntu 根文件系统包含 apt,可以在后续按需下载需要的软件包,相较于 busybox、buildroot 而言,功能会更加丰富。

这里给出两种方式:

1. 使用自动构建 Ubuntu 根文件系统脚本

参考 https://github.com/LubanCat/ubuntu 。

2. 自制 ubuntu-base 根文件系统

wget http://cdimage.ubuntu.com/ubuntu-base/releases/20.04/release/ubuntu-base-20.04.2-base-riscv64.tar.gz

mkdir rootfs

dd if=/dev/zero of=riscv_rootfs.img bs=1M count=1024 oflag=direct

mkfs.ext4 riscv_rootfs.img

sudo mount -t ext4 riscv_rootfs.img rootfs/

sudo tar -xzf ubuntu-base-20.04.2-base-riscv64.tar.gz -C rootfs/

sudo cp /path-to-qemu/build/qemu-system-riscv64 rootfs/usr/bin/

sudo cp /etc/resolv.conf rootfs/etc/resolv.conf

sudo mount -t proc /proc rootfs/proc

sudo mount -t sysfs /sys rootfs/sys

sudo mount -o bind /dev rootfs/dev

sudo mount -o bind /dev/pts rootfs/dev/pts

sudo chroot rootfs

# chroot 进入 rootfs 后,安装必要的软件包:

apt-get update

apt-get install git sudo vim bash-completion kmod net-tools iputils-ping resolvconf ntpdate

exit

sudo umount rootfs/proc

sudo umount rootfs/sys

sudo umount rootfs/dev/pts

sudo umount rootfs/dev

sudo umount rootfs

五、Rust 环境配置

请参考 Rust 语言圣经。

六、编译运行 hvisor

1. 准备 hvisor 源码和必要文件

将 hvisor 代码仓库 克隆到本地。

git clone https://github.com/syswonder/hvisor.git

在 hvisor/platform/riscv64/{BOARD}/image 文件夹下添加 Linux Image、根文件系统等等。

BOARD 为 qemu-plic, 如果要在 qemu-aia 平台上执行,则将 BOARD 为 qemu-aia。

将之前编译好的根文件系统、Linux 内核镜像分别放在 virtdisk、kernel 目录下,并分别重命名为 rootfs1.ext4、Image,它们在 Makefile 中指定了,你也可以修改 Makefile 中的内容。

2. 编译设备树

# 编译设备树

make BID=riscv64/{BOARD} dtb

3. 编译并运行 hvisor

在 hvisor 目录下,根据需要执行下列命令:

# 对于 qemu-plic board 执行

make run ARCH=riscv64 BOARD=qemu-plic

# 对于 qemu-aia board 执行

make run ARCH=riscv64 BOARD=qemu-aia

注意: Makefile 中的启动命令中包含了 -S 参数,可以看做 Qemu 虚拟机启动时的一个断点,需要 Qemu 收到 continue 才可以继续执行,这时可以方便地查看 /dev/pts/xxx, 可以把它看做是 Qemu 提供的 virtio-console 暴露给 Host 使用的虚拟串口设备。

你可以看到类似以下内容:

char device redirected to /dev/pts/4 (label serial3)

然后,同时按下 ctrl+a, 随后输入 c,回车,即可继续执行,随后会打印 OpenSBI + Hvisor + Linux 的输出信息。

为了使用上述的虚拟串口,你需要新建一个终端,然后可以通过如下命令连接它:

screen /dev/pts/xxx

注意:Qemu 只提供一个物理串口,当启动两个 zone 并且两个 zone 各自占用一个串口时,就需要使用到该虚拟串口设备。

4. 启动 non-root linux

注意:Non-root 使用设备有两种方式,设备直通和 virtio,其中 virtio 设备的后端在 root zone(linux)。

对于 hvisor,我们提供了管理程序 hvisor-tool,具体请参考 hvisor-tool 的 README。

对于 riscv 架构来说,编译 hvisor-tool 时,建议除了上述下载的交叉工具链外,另外使用 ubuntu apt 安装 riscv64-linux-gnu-gcc。

例如,若要编译面向 riscv 架构的命令行工具,且 Hvisor 环境中的 Linux 镜像编译来源的源码位于 ~/linux,则可执行:

make all ARCH=riscv LOG=LOG_INFO KDIR=~/linux

请务必保证 Hvisor 中的 Root Linux 镜像是由编译 hvisor-tool 时参数选项中的 Linux 源码目录编译产生。

编译完成后,将 output/hvisor.ko、output/hvisor 复制到 hvisor/platform/riscv64/{BOARD}/image/virtdisk/rootfs1.ext4 根文件系统中,你可以先将 rootfs1.ext4 挂载后进行拷贝。

再将 zone1 的内核镜像(如果是与 zone0 相同的 Linux 内核,则复制一份 {BOARD}/image/kernel/Image 即可)、设备树({BOARD}/image/dts/linux2.dtb)、配置文件({BOARD}/configs/zone1-linux.json等)拷贝到 rootfs1.ext4 根文件系统中,你可以将它们重命名为 Image、linux2.dtb、linux2.json 等(与 .json 里面的文件名匹配即可)。

除此之外,还需要为 Zone1 linux 制作一个根文件系统。可以将 {BOARD}/image/virtdisk 中的 rootfs1.ext4 复制一份,也可以重新制作根文件系统(最好改小镜像大小),并改名为 riscv_rootfs2.img(和 .json 里面的文件名匹配即可)。之后将 riscv_rootfs2.img 放入 rootfs1.ext4 根文件系统中。

对于 BOARD=qemu-plic,启动 root linux 后,你可以按照如下方式启动 non-root linux:

insmod hvisor.ko

rm nohup.out

mkdir -p /dev/pts

mount -t devpts devpts /dev/pts

nohup ./hvisor zone start zone1-linux.json && cat nohup.out | grep "char device" && script /dev/null

对于 BOARD=qemu-aia,启动 root linux 后,你可以按照如下方式启动 non-root linux:

insmod hvisor.ko

mount -t proc proc /proc

mount -t sysfs sysfs /sys

rm nohup.out

mkdir -p /dev/pts

mount -t devpts devpts /dev/pts

nohup ./hvisor virtio start zone1-linux-virtio.json &

./hvisor zone start zone1-linux.json && \

cat nohup.out | grep "char device" && \

script /dev/null

注意:它们的区别在于配置不同,你可以修改配置,以自定义使用设备直通还是 virtio,以当前 hvisor 中的默认配置为例:

-

qemu-plic 采用的是直通的设备(尽管启动命令中为 virtio 设备,这里可以看做是直通,因为它由 Qemu 提供设备后端)

-

qemu-aia 采用了 virtio,由 root linux 提供 virtio 设备后端(non-root 的 virtio 驱动会被拦截转发到 root linux 的 virtio 后端)

在 QEMU x86_64 上运行 Hvisor

一、环境准备

硬件

- 具有 Intel CPU 的计算机

- 支持 VT-x,并已在 BIOS 启用

软件

- 使用 Ubuntu 等 Linux 操作系统,以下示例基于 WSL2 Ubuntu 24.04 LTS

二、安装 gcc 编译器

sudo apt update

sudo apt install gcc

三、安装 QEMU

推荐自行编译 QEMU,便于日后修改 QEMU 源码进行调试。此处以 QEMU v9.2.3 为例,也可以安装更新的版本。

# 安装依赖

sudo apt install git libglib2.0-dev libfdt-dev libpixman-1-dev zlib1g-dev \

ninja-build python3-venv bzip2 make

# 获取 QEMU 源码

wget https://download.qemu.org/qemu-9.2.3.tar.xz

# 解压

tar xvJf qemu-9.2.3.tar.xz

# 进入源码目录

cd qemu-9.2.3/

# 生成配置并编译

./configure --enable-kvm --enable-slirp --target-list=x86_64-softmmu

# 编译 qemu

make -j$(nproc)

编辑 ~/.bashrc 文件,在末尾加入:

export PATH="/path/to/qemu-9.2.3/build:$PATH"

随后在终端执行 source ~/.bashrc 更新环境变量,或者重启一个新终端。使用 qemu-system-x86_64 --version 确认当前 QEMU 版本,若为 9.2.3 则安装成功。

四、编译 Linux Kernel

以 Linux v5.19 为例。

# 安装依赖

sudo apt install flex bison libelf-dev libssl-dev

# 下载 linux 5.19 源码

git clone https://github.com/torvalds/linux -b v5.19 --depth=1

cd linux

git checkout v5.19

# 生成默认的编译配置

make ARCH=x86_64 defconfig

# 启用 X2APIC 及其依赖项

./scripts/config --enable CONFIG_X86_X2APIC

./scripts/config --enable CONFIG_ACRN_GUEST

# 启用 RAM 块设备支持

./scripts/config --enable CONFIG_BLK_DEV_RAM

# 启用 IPV6、BRIDGE 和 TUN,以支持在 root linux 中创建网桥和 tap 设备

./scripts/config --enable CONFIG_IPV6

./scripts/config --enable CONFIG_BRIDGE

./scripts/config --enable CONFIG_TUN

# 启用 VIRTIO MMIO,以支持 non-root linux 使用 virtio 驱动

./scripts/config --enable CONFIG_VIRTIO_MMIO

./scripts/config --enable CONFIG_VIRTIO_MMIO_CMDLINE_DEVICES

# 关闭编译期间将警告视为报错

./scripts/config --disable CONFIG_WERROR

# 编译,遇到选项一直 Enter 即可

make ARCH=x86_64 -j$(nproc)

五、基于 Ubuntu 22.04 构建根文件系统

# 下载 Ubuntu 镜像

wget http://cdimage.ubuntu.com/ubuntu-base/releases/22.04/release/ubuntu-base-22.04.5-base-amd64.tar.gz

# 创建 rootfs,用于挂载 rootfs1.img

mkdir -p rootfs

# 创建一个 2G 大小的 ubuntu.img,可以修改 count 修改 img 大小

dd if=/dev/zero of=rootfs1.img bs=1M count=2048 oflag=direct

# 格式化为 ext4 文件系统

mkfs.ext4 rootfs1.img

# 挂载 rootfs1.img

sudo mount -t ext4 rootfs1.img rootfs/

# 将 ubuntu.tar.gz 的内容解压到 rootfs

sudo tar -xzf ubuntu-base-22.04.5-base-amd64.tar.gz -C rootfs/

# 让 rootfs 绑定和获取物理机的一些信息和硬件

sudo cp /etc/resolv.conf rootfs/etc/resolv.conf

sudo mount -t proc /proc rootfs/proc

sudo mount -t sysfs /sys rootfs/sys

sudo mount -o bind /dev rootfs/dev

sudo mount -o bind /dev/pts rootfs/dev/pts

# 将文件系统切换到 rootfs

sudo chroot rootfs

# 在 rootfs 中安装必要的软件包

apt update

apt install git sudo vim bash-completion \

kmod net-tools iputils-ping resolvconf ntpdate screen \

pciutils iproute2 isc-dhcp-client systemd bridge-utils

# 创建进入根文件系统时执行的 init 脚本,赋予执行权限

touch init

chmod 777 init

# 修改 init 脚本,具体内容如下:

# ======================= init =======================

#!/bin/sh

mount -t proc none /proc

mount -t sysfs none /sys

mkdir -p /dev/pts

mount -t devpts none /dev/pts

echo

echo "Hello Zone 0!"

echo "This boot took $(cut -d' ' -f1 /proc/uptime) seconds"

echo

script /dev/null -c "hostname zone0 && su"

# ====================================================

# 退出 rootfs

exit

# 卸载 rootfs

sudo umount rootfs/proc

sudo umount rootfs/sys

sudo umount rootfs/dev/pts

sudo umount rootfs/dev

sudo umount rootfs

六、Rust 环境配置

请参考 Rust 语言圣经。

七、编译并运行 Hvisor,进入 zone0 Linux

# 下载到本地

git clone https://github.com/syswonder/hvisor.git

cd ./hvisor

# 安装依赖

sudo apt install grub-common xorriso grub-efi-amd64 mtools ovmf

# 新建 kernel 文件夹,用于放置 Linux kernel

mkdir -p ./platform/x86_64/qemu/image/kernel

# 将第四步编译的 Linux kernel 复制到 kernel 文件夹

LINUX_PATH="<路径>/linux"

cp "${LINUX_PATH}/arch/x86/boot/setup.bin" ./platform/x86_64/qemu/image/kernel/

cp "${LINUX_PATH}/arch/x86/boot/vmlinux.bin" ./platform/x86_64/qemu/image/kernel/

# 新建 virtdisk 文件夹,用于放置根文件系统

mkdir -p ./platform/x86_64/qemu/image/virtdisk

# 将第五步制作的根文件系统 rootfs1.img 复制到 virtdisk 文件夹

ROOTFS1_PATH="<路径>/rootfs1.img"

cp "${ROOTFS1_PATH}" ./platform/x86_64/qemu/image/virtdisk/

# 运行 Hvisor

make ARCH=x86_64 BOARD=qemu run

请注意

若执行 `make BOARD=qemu run` 遇到如下报错:

Could not access KVM kernel module: Permission denied

qemu-system-x86_64: -accel kvm: failed to initialize kvm: Permission denied

执行 sudo usermod -a -G kvm 你的用户名 加入 kvm 的用户组,重启终端后再次尝试。

八、使用 hvisor-tool 运行 zone1 Linux

完成最新版本的 hvisor-tool 的编译,具体请参考 hvisor-tool 的 README。

git clone https://github.com/syswonder/hvisor-tool.git

cd hvisor-tool

# KDIR 必须设为第四步编译的 Linux kernel 根目录

make all ARCH=x86_64 LOG=LOG_INFO KDIR=linux根目录

编译完成后,需要将 hvisor-tool 的可执行文件 tools/hvisor 和内核模块 driver/hvisor.ko 复制到 zone0 的根文件系统中的指定位置,例如 /,将 zone1 的根文件系统、内核镜像以及配置文件放在同一目录。具体的文件名需要与 hvisor-tool 配置文件(来自 hvisor-tool 的 examples/qemu-x86_64/virtio_cfg.json 和 examples/qemu-x86_64/zone1_linux.json)的内容保持一致。

LINUX_PATH="<路径>/linux"

HVISOR_PATH="<路径>/hvisor"

HVISOR_TOOL_PATH="<路径>/hvisor-tool"

ROOTFS2_PATH="<路径>/rootfs2.img"

# 回到创建根文件系统时的目录,挂载

sudo mount -t ext4 rootfs1.img rootfs/

# 复制 hvisor-tool 的 driver/hvisor.ko 和 tools/hvisor

sudo cp "${HVISOR_TOOL_PATH}/driver/hvisor.ko" rootfs/hvisor.ko

sudo cp "${HVISOR_TOOL_PATH}/tools/hvisor" rootfs/hvisor

# 复制 zone1 的配置文件到 root 路径下

sudo cp "${HVISOR_TOOL_PATH}/examples/qemu-x86_64/virtio_cfg.json" \

rootfs/virtio_cfg.json

sudo cp "${HVISOR_TOOL_PATH}/examples/qemu-x86_64/zone1_linux.json" \

rootfs/zone1_linux.json

# 复制 zone1 的根文件系统和内核镜像,文件系统的制作见下文,

# 内核镜像可以直接沿用第四步所得

sudo cp "${ROOTFS2_PATH}" \

rootfs/rootfs2.img

sudo cp "${LINUX_PATH}/arch/x86/boot/setup.bin" \

rootfs/setup.bin

sudo cp "${LINUX_PATH}/arch/x86/boot/vmlinux.bin" \

rootfs/vmlinux.bin

# 复制内核跳板,需要 Hvisor 已经编译过一次

sudo cp "${HVISOR_PATH}/platform/x86_64/qemu/image/bootloader/out/boot.bin" \

rootfs/boot.bin

# 修改 init,新增内容如下:

# ======================= init =======================

echo "This boot took $(cut -d' ' -f1 /proc/uptime) seconds"

echo

...

ifconfig eth0 up

dhclient eth0

brctl addbr br0

brctl addif br0 eth0

ifconfig eth0 0

dhclient br0

ip tuntap add dev tap0 mode tap

brctl addif br0 tap0

ip link set dev tap0 up

insmod hvisor.ko

...

script /dev/null -c "hostname zone0 && su"

# ====================================================

# 卸载

sudo umount rootfs

# 需要将新的 rootfs1.img 移动至 Hvisor 中

ROOTFS1_PATH="<路径>/rootfs1.img"

cp "${ROOTFS1_PATH}" ./platform/x86_64/qemu/image/virtdisk/

zone1 根文件系统的制作可以参考第五步,不用安装额外的依赖包。但需要适当缩减容量(例如 1G),使之能够放入 zone0 的根文件系统中。zone1 的 init 脚本内容如下:

#!/bin/sh

mount -t proc none /proc

mount -t sysfs none /sys

mkdir -p /dev/pts

mount -t devpts none /dev/pts

echo

echo "Hello Zone 1!"

echo "This boot took $(cut -d' ' -f1 /proc/uptime) seconds"

echo

ip link set eth0 up

dhclient eth0

script /dev/null -c "hostname zone1 && su"

回到 Hvisor 的根目录,执行下述指令,即可进入 zone1 Linux

# 运行 Hvisor,进行 zone0

make ARCH=x86_64 BOARD=qemu run

# 启动 hvisor-tool virtio 设备

nohup ./hvisor virtio start virtio_cfg.json &

# 启动 zone1

./hvisor zone start ./zone1_linux.json

# 切换到 zone1 的终端,xxx 一般为 1

screen /dev/pts/xxx

在龙芯 3A5000主板(7A2000)上启动 hvisor

第一步:获取 hvisor 源码并进行编译

首先需要安装龙芯新世界 ABI 的 loongarch64-unknown-linux-gnu- 工具链,请从 https://github.com/sunhaiyong1978/CLFS-for-LoongArch/releases/download/8.0/loongarch64-clfs-8.0-cross-tools-gcc-full.tar.xz 下载并解压到本地,然后请将 cross-tools/bin 目录添加到你的 PATH 环境变量中,保证 loongarch64-unknown-linux-gnu-gcc 等工具可以被 shell 直接调用。

然后克隆代码到本地:

git clone https://github.com/enkerewpo/hvisor

make BID=loongarch64/ls3a5000

编译完成后在 target 目录下可以找到 strip 之后的 hvisor.bin 文件。

第二步(不自己编译 buildroot/linux 等):获取 rootfs/内核镜像

请从 https://github.com/enkerewpo/linux-hvisor-loongarch64/releases 下载最新发布的 hvisor 默认龙芯 linux 镜像(包括 root linux kernel+root linux dtb+root linux rootfs,其中 root linux rootfs 中包括 non root linux+nonroot linux dtb+nonroot linux rootfs)。rootfs 中已打包好 nonroot 的启动 json 以及 hvisor-tool、内核模块等。

第二步(自己编译 buildroot/linux 等):完整编译 rootfs/内核镜像

如果你需要自己编译,这个流程将会较为复杂,接下来将介绍相关细节:

1. 准备好环境

创建一个工作目录(可选):

mkdir workspace && cd workspace

git clone https://github.com/enkerewpo/hvisor

git clone https://github.com/enkerewpo/buildroot-loongarch64

git clone https://github.com/enkerewpo/linux-hvisor-loongarch64 hvisor-la64-linux

git clone https://github.com/enkerewpo/hvisor-tool

git clone https://github.com/enkerewpo/hvisor_uefi_packer

2. 准备 buildroot 环境

因为 buildroot 在找不到需要编译的 package 时会从各个地方下载源码压缩包,这里我准备好了一个预下载的镜像:

https://pan.baidu.com/s/1sVPRt0JiExUxFm2QiCL_nA?pwd=la64

下载后将 dl 目录放在 buildroot-loongarch64 根目录即可,或者你也可以不下载,让 buildroot 自动下载(可能会非常慢)。如果你在解压了 dl 目录后发现编译时仍然有软件包需要下载,也是正常现象。

3. 编译 buildroot

cd buildroot-loongarch64

make loongson3a5000_hvisor_defconfig

make menuconfig # 请将 Toolchain/Toolchain path prefix 设置为你本地的 loongarch64 工具链路径和前缀

# 然后选择右下角 save 保存到 .config 文件

make -j$(nproc)

请注意

这个过程可能持续数小时,取决于你的机器性能和网络环境。

编译完成后,在 output/images 中可以找到 rootfs.cpio.gz 文件,请牢记这个文件的路径,这是一个基本的 rootfs。

下一步请手动将这个路径(设为 ROOTFS_CPIO_GZ_PATH)软连接到 hvisor-la64-linux/rootfs/buildroot/rootfs.cpio.gz,该位置存放的 rootfs 文件将通过 ./build nonroot_setup 命令生成一个精简版的 nonroot rootfs。

如果你希望自己制作 root 和 nonroot 的 rootfs,可以不进行这一步,请注意这会导致 make world 流程中无法自动生成 nonroot rootfs。

4. 第一次编译 linux(为后续 make world 做准备)

一些前置知识:

- linux 源码目录内

arch/loongarch/configs为 defconfig 目录,你可以在仓库中找到 root 和 nonroot 分别的 defconfig。 - linux 源码目录内

arch/loongarch/boot/dts为 dts 目录,你可以在仓库中找到 root 和 nonroot 分别的 dts 文件,其中带linux1.dts等字样的文件为通过下面./build zone ...命令使用的以 zone name 为索引来进行 dts 内嵌,linux1,linux2,linux3为默认的三个 nonroot zone name。

cd hvisor-la64-linux

echo "6.11.6" > chosen_root # 选择 linux-6.11.6 目录作为 root linux 的编译源码

echo "6.13.7" > chosen_nonroot # 选择 linux-6.13.7 目录作为 nonroot linux 的编译源码,

# 你也可以选择其他版本例如 6.11.6 git,请保证对应的 linux-{suffix} 目录存在

./build def root/nonroot # 生成默认 root linux 的 defconfig

./build menu root/nonroot # 进入 menuconfig 配置 root linux 的配置

./build kernel root # 编译 root linux

./build zone {type} {name} {entry}

# type=root/nonroot name=zone_name(此name也用于选择对应加载的{zone_name}.dts 文件)

# entry=vmlinux 的 entry 地址,用于 DMA 支持

对于 build 脚本支持的更多命令(例如后文 make world 流程中涉及到的动态修改 linkerscript load addr 以及配置 target output 的 zone name 等功能,请运行 ./build --help 查看)。

请注意,目前仓库的默认 defconfig 均关闭了 initramfs 的 rootfs 内嵌选项,你可能需要检查一下 configs 目录中的 root 和 nonroot defconfig 并按你的需求进行修改(通过 ./build def root/nonroot 命令生成后再运行 ./build menu root/nonroot 进行修改,请注意如果你之后要使用 make world,这里必须保存一次 defconfig ./build save root/nonroot 将 .config 文件保存到 configs 目录下,供后续 make world 使用,因为make world会直接从configs目录下读取 defconfig,如果不运行 save 的话将会导致你的临时 .config 被覆盖)。

请注意,目前仓库的默认 dts 可能不适合你本地的环境,其中对于 UART 节点请根据需要进行修改(例如 3A6000 支持主板背板的 COM1,则你可以 enable COM1 节点并让 zone 使用,或者使用 3A5000 和 3A6000 均支持的主板 DEBUG pin 底座接 UART0 输出)。

请注意

编译内核过程可能持续几十分钟,取决于你的机器性能。

附:如何通过 menuconfig 配置 initramfs 并添加 rootfs:

- 在 hvisor-la64-linux 目录下运行

./build def root/nonroot生成 defconfig,然后运行./build menu root/nonroot进入 menuconfig 配置。 - 在 menuconfig 中找到 General setup 中的

Initial RAM filesystem and RAM disk (initramfs/initrd) support选项,启用。 - 此时会多出一个

Initramfs source file(s)选项,在这里输入你想要添加的 rootfs 路径,例如PATH_TO_ROOTFS/rootfs.cpio.gz。 - 保存退出,然后运行

./build kernel root/nonroot编译内核,运行./build save root/nonroot保存 defconfig 到仓库。

附:如何控制 console 是使用 virtio-console 还是走默认的 UART(UART0、COM1): 请检查或修改你的 root 或 nonroot 的 rootfs,进入 /etc 目录,其中需要有两个关键文件:

inittab文件,对于 root 和 nonroot 的一些示例见 https://github.com/enkerewpo/buildroot-loongarch64/tree/master/board/loongson/ls3a5000/rootfs_ramdisk_overlay/etcprofile文件,你可以在这里控制 shell login 时运行哪些初始化脚本,一个参考:https://github.com/enkerewpo/buildroot-loongarch64/blob/master/board/loongson/ls3a5000/rootfs_ramdisk_overlay/etc/profile- 对于

./build nonroot_setup命令,请参考./build脚本里相关流程,以及HVISOR_LA64_LINUX_DIR/rootfs/nonroot_inittab和HVISOR_LA64_LINUX_DIR/rootfs/nonroot_profile文件,这两个文件将会在构造 trimmed rootfs for nonroot 时,被./build nonroot_setup命令自动替换默认的inittab和profile文件,请注意,仓库中的默认 inittab 配置为挂载到hvc0上,即 nonroot 的 shell 自动 getty 到 virtio-console,在启动 nonroot 时,你将会在串口看到启动 console 的日志,在进入 shell 后串口不再有输出,为正常现象,此时在 root 中 screen 到 nonroot 的 pts 后,你将会看到 nonroot 的 shell 输出并进行交互。

5. 通过 hvisor uefi packer 执行 make world 流程

cd hvisor_uefi_packer

make menuconfig # 生成 .config,你可以参考 configs 目录下的一些示例配置的格式

vim zones.json # 由于 hvisor 暂未支持 iommu,对于 PCIe 设备的 DMA,

# 必须要求 GPA=HPA,所以每一个虚拟机的 vmlinux 编译时会自动修改 load addr 以避免 GPA/HPA 冲突

./make_world # 这个过程将会很慢,请耐心等待

如果你只需要一个 nonroot,请修改 zones.json,添加或删除对应的配置。下面简述标准流程中 make world 会做哪些事情:

- 从你配置好的

.config中读取相关信息:- hvisor 源码路径

HVISOR_SRC_DIR - hvisor-tool 源码路径

HVISOR_TOOL_DIR - buildroot 源码路径

BUILDROOT_DIR - hvisor la64 linux 仓库源码路径

HVISOR_LA64_LINUX_DIR

- hvisor 源码路径

- 读取

HVISOR_LA64_LINUX_DIR/chosen_root和HVISOR_LA64_LINUX_DIR/chosen_nonroot中的内容,分析选取对应源码版本。 - 读取当前目录下的

zones.json文件,获取需要编译的 zone 配置。 - 编译 hvisor-tool(由于内核模块需要对应的源码,这里编译 hvisor-tool 会固定使用前面解析到的 chosen_root 源码作为

KDIR编译内核模块),并把生成的hvisor命令行工具和hvisor.ko内核模块拷贝到BUILDROOT_DIR/rootfs_ramdisk_overlay/tool目录下,此目录将会被 buildroot 下次编译时打包进 rootfs。 - 在

HVISOR_LA64_LINUX_DIR下运行./build nonroot_setup命令,生成 nonroot rootfs(即不包含/toolhvisor 资源目录等文件的一个较为纯净的 nonroot rootfs),请参考前面章节的部分对 buildroot 生成的 rootfs 进行软连接。该命令生成的精简 rootfs 位于HVISOR_LA64_LINUX_DIR/rootfs/nonroot_rootfs.cpio.gz,可供使用。 - 在

HVISOR_LA64_LINUX_DIR下运行./build def nonroot,生成 nonroot linux 的 defconfig。 - 根据

zones.json中的配置,依次编译各个 nonroot zone,并复制到BUILDROOT_DIR/rootfs_ramdisk_overlay/tool/nonroot目录下,此目录将会被 buildroot 下次编译时打包进 rootfs。 - 然后进行一次 buildroot 的编译,前面提到的相关文件均会被打包进

rootfs.cpio.gz文件中。 - 进入

HVISOR_LA64_LINUX_DIR目录,运行./build def root与./build kernel root生成 root linux 的 vmlinux 文件,请在编译后检查HVISOR_LA64_LINUX_DIR/target目录。

至此 make world 流程结束。一些注意事项:

- zones.txt 写好的 zone name 将会最终对应 dts 目录内对应的 {zone name}.dts 文件作为内嵌到 vmlinux 的设备树文件。

- 你可能需要调整相关的 defconfig 和 dts,仓库中的最新文件由于目前仍在开发中不停更新,其可能不适合你的实际需求。

- 如果你希望修改 zone 启动时的 cmdline,请修改对应的设备树中的 bootargs 字段。

如果可以的话,请打开或 unpack 生成的 rootfs.cpio.gz 文件,检查其中是否包含如下结构,如果缺少任何文件,请检查你的编译流程是否正确。

/ # 根目录

├── daemon.sh # 启动 virtio 后端的脚本

├── start.sh # 启动 nonroot 虚拟机的脚本

└── tool/ # hvisor 资源文件夹

├── hvisor # hvisor 命令行工具

├── hvisor.ko # hvisor 内核模块

├── linux*-json # 虚拟机 linux* 启动配置文件

├── linux*-disk.ext4 # 虚拟机 linux* virtio-blk 文件系统镜像

├── virtio_cfg.json # 虚拟机 virtio 配置文件

└── nonroot/ # nonroot 虚拟机 vmlinux.bin 目录

└── vmlinux-*.bin # 虚拟机内核映像文件,以 zone name 为后缀的 bin 是通过 ./build zone 命令得到的

第三步:编译 UEFI 镜像

由于 3A5000 以及之后的 3 系 CPU 的主板均采用 UEFI 启动,所以只能通过 efi 镜像的方法启动 hvisor。

./make_loongarch64 # 读取 .config 中配置的相关路径和信息,生成 BOOTLOONGARCH64.EFI

此时会在 hvisor_uefi_packer 目录下生成 BOOTLOONGARCH64.EFI,将其放在 U 盘的第一个 FAT32 分区的 /EFI/BOOT/BOOTLOONGARCH64.EFI 位置。

请注意

当你自己编译 root 和 nonroot linux 时,请手动 readelf 得到两个 vmlinux 的 entry 地址,并在 board.rs 以及 linux1/2/3.json 中对应写好,否则一定会启动失败,前文中提到的 make_loongarch64 脚本会帮你自动进行这一检查。

第四步:上板启动

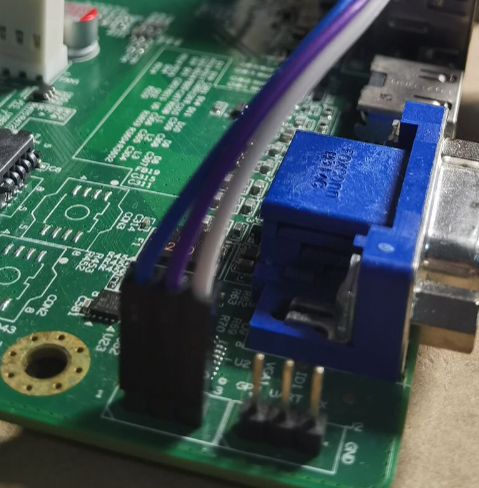

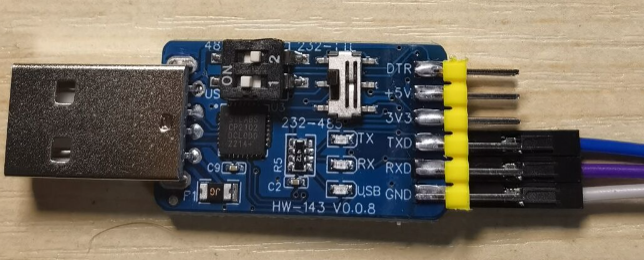

3A5000 主板 CPU UART0 连接

请参考下图中的连线将 3A5000 主板的 UART0 连接到你的串口转接器上(CPU UART0 引脚位于 VGA connector 旁边):

其中从左到右(图中三角形标识的一端为 1 号引脚 RX)分别为 RX(1)、TX(2)、GND(3) 三个引脚,分别对应连接到你的 USB 转接器的 TX、RX、GND 引脚上,如图所示:

请注意

请将串口转接器配置为 RS232 电压模式,以及 USB 串口转接器的 TX 接主板 RX、RX 接主板 TX、GND 接主板 GND(可不接地)。

主板开机

主板上电开机,按 F12 进入UEFI Boot Menu,在目录选择 U 盘启动,即可进入 hvisor,然后自动进入 root linux。 如果您接入了 VGA 屏幕,也可以看到启动最开始的一部分 UEFI loader 的日志输出,之后将转为通过 UART0 输出(hvisor 以及 root/nonroot linux 均使用串口进行输入和输出)。

启动 nonroot

启动后在串口端可以看到 hvisor 的 log 以及 root linux 的 bash,输入:

./daemon.sh

./start.sh 1/2/3 # 启动 nonroot,之后请手动运行 screen /dev/pts/0 or 1, 2

# (linux1-pts0, linux2-pts1, linux3-pts2 by default)

之后会自动启动 nonroot(一些相关配置文件位于 root linux 的 /tool 目录内,包括提供给 hvisor-tool 的 nonroot zone 配置 json 以及 virtio 配置 json 文件),启动 nonroot 后在 root linux 终端输入 screen /dev/pts/0 或 screen /dev/pts/1 或 screen /dev/pts/2 (分别对应 linux1-pts0, linux2-pts1, linux3-pts2 三个 pts),你会看到一个打印了 nonroot 字样的 bash 出现,你可以在使用 screen 时按 CTRL+A D 快捷键 detach(请记住显示的 screen session 名称 / ID),此时会返回 root linux,如果希望返回 nonroot linux,则运行

screen -r {刚才的 session 全名或者只输入最前面的 PID}

之后会返回 nonroot linux 的 bash。

在 NUC 14 Essential x86_64 上运行 Hvisor

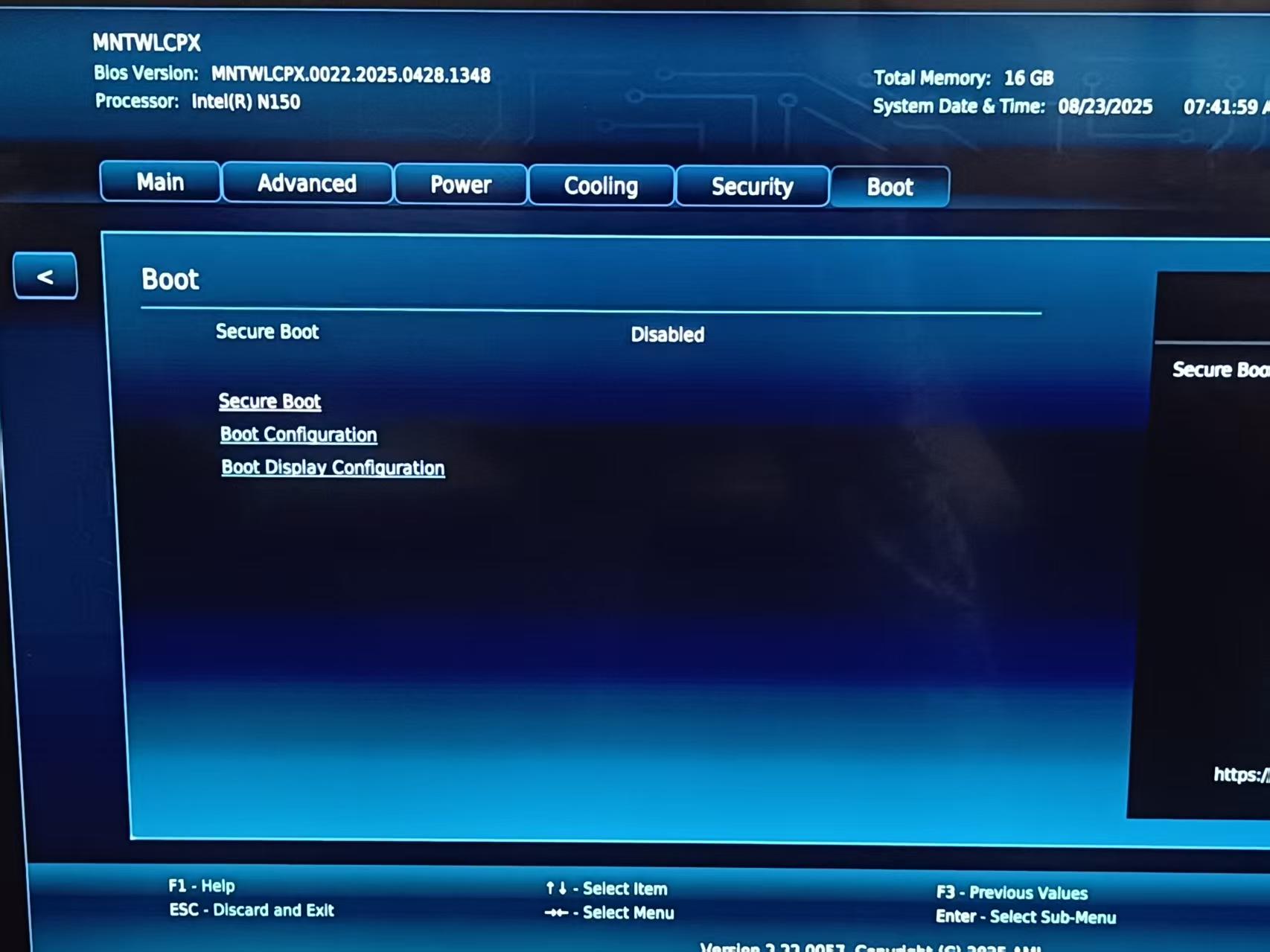

一、BIOS 设置

NUC14 初始自带一个 BIOS,需要进行相应设置。

完成必要的连线工作后(电源、显示器、路由器),开机,按 F8(可能有所不同)进入 BIOS,打开 Boot 页面,关闭 Secure Boot。此后即可加载自制的镜像。

二、编译 Linux 内核

在 Qemu X86_64 编译内核的基础上,增加下述配置项,然后重新编译:

# nvme 磁盘驱动

./scripts/config --enable CONFIG_NVME_CORE

./scripts/config --enable CONFIG_BLK_DEV_NVME

# vesafb 图形显示器驱动

./scripts/config --enable CONFIG_FB

./scripts/config --enable CONFIG_FB_CMDLINE

./scripts/config --enable CONFIG_FB_VESA

三、制作启动盘

为了测试方便,本文选择一块 U 盘作为 Hvisor 的启动盘,并且在上面安装 GRUB 作为 bootloader。

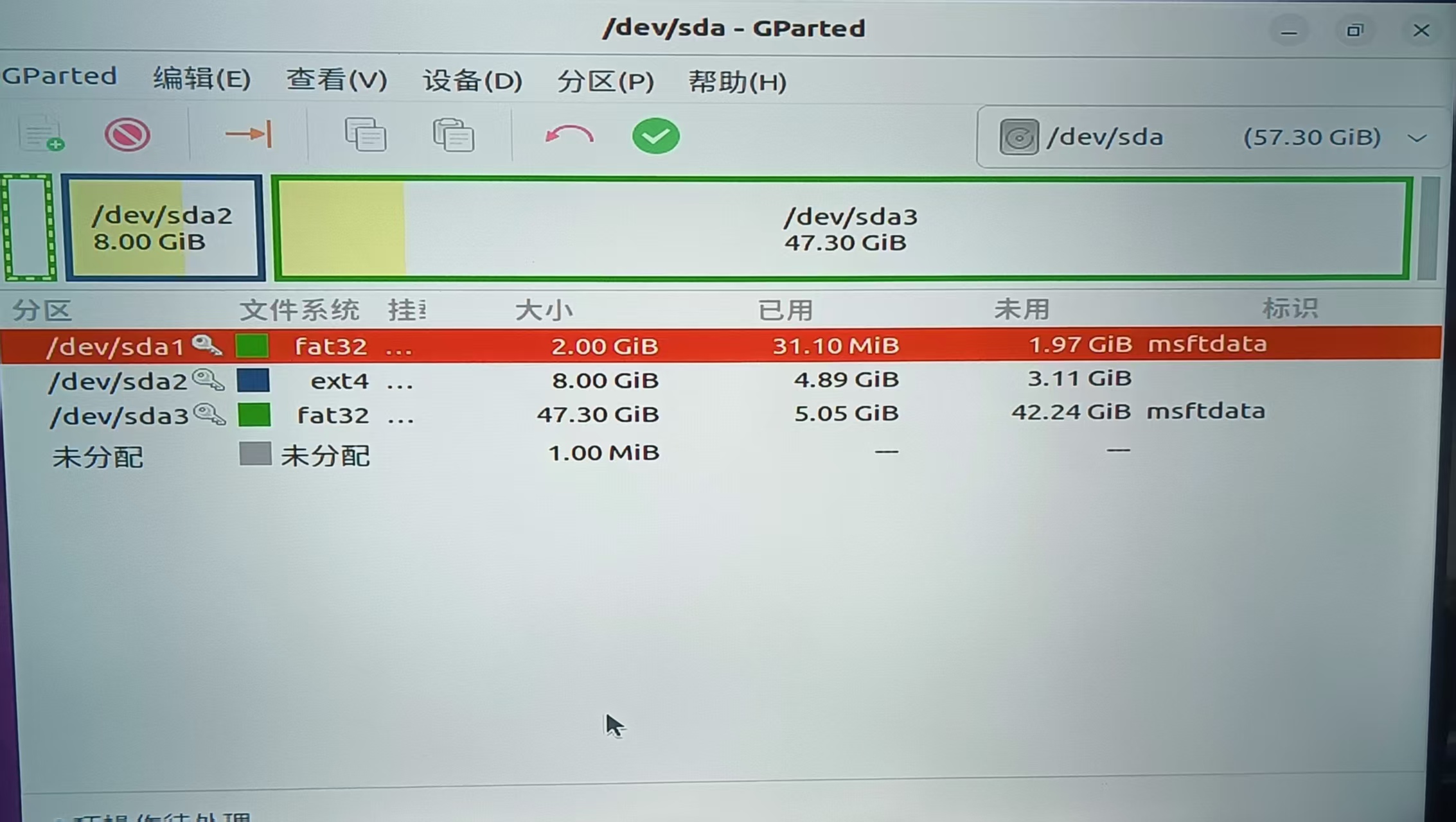

首先需要对 U 盘进行分区,推荐使用带有图形界面的 Linux 操作系统以及分区工具 GParted。U 盘插入后,会对应到一个设备节点,例如 /dev/sda。在正式开始分区前,确保 U 盘内无重要数据或者已经备份。

打开 GParted,选择 U 盘作为当前盘,然后点击 Device → Create Partition Table... 建立一个 GPT 分区表。如果提示无法建立分区表,需要使用 umount 卸载所有活动分区,然后重新启动 GParted。

建完 GPT 分区表后,新建一个 EFI 分区,该分区必须为 FAT32 格式。然后再新建一个文件系统分区作为 zone0 的根文件系统,分区格式为 EXT4。建立好分区后,点击绿色的 √,正式完成划分。在下图的示例中,FAT32 分区被命名为 /dev/sda1,EXT4 分区被命名为 /dev/sda2。不同环境下的命名可能有所不同,需要留意。

接下来进行 GRUB 的编译。

# 下载 GRUB

wget https://ftp.gnu.org/gnu/grub/grub-2.06.tar.xz

# 解压并打开

tar -xf grub-2.06.tar.xz

cd grub-2.06/

# 配置并编译

mkdir EFI64

cd EFI64

../configure CFLAGS="-Wno-error" --target=x86_64 --with-platform=efi && make -j$(nproc)

然后将 GRUB 安装到 U 盘的 EFI 分区中。

# 将 EFI 分区 mount 到 mnt 文件夹

sudo mount /dev/sda1 /mnt

# 安装到 /mnt

cd ../EFI64/grub-core

sudo ../grub-install -d $PWD --force --removable --no-floppy --target=x86_64-efi --boot-directory=/mnt/boot --efi-directory=/mnt

四、编译 Hvisor

进入 Hvisor 所在路径,打开 platform/x86_64/nuc14mnk/board.rs,将 ROOT_ZONE_CMDLINE 中 root=/dev/sda2 参数修改为 EXT4 分区的名字。

由于 NUC14 未提供串口接口,若要打印调试日志,需要在 platform/x86_64/nuc14mnk/cargo/features 添加 graphics 这一特性,使得日志可以直接绘制在显示器上,这一特性仅供早期调试。

参考 QEMU 的步骤,将构建好的内核文件和根文件系统移动到指定位置。执行编译指令 make ARCH=x86_64 BOARD=nuc14mnk。

可以看到 /platform/x86_64/nuc14mnk/image/iso/boot 路径下有文件生成,将 boot 文件夹整个复制到第三步的 /mnt 中。此时 EFI 分区的大致布局如下:

.

├── boot

│ ├── grub

│ │ ├── fonts

│ │ ├── grub.cfg # 用于配置 GRUB 菜单的各个选项

│ │ ├── grubenv

│ │ ├── locale

│ │ └── x86_64-efi

│ │ ├── acpi.mod

│ │ ├── ...

│ │ └── zstd.mod

│ ├── hvisor

│ └── kernel

│ ├── boot.bin

│ ├── setup.bin

│ └── vmlinux.bin

└── EFI

└── BOOT

└── BOOTX64.EFI

grub.cfg 可以配置 Hvisor 加载时的相关操作,其 menuentry 具体如下。multiboot2 会将 Hvisor 以 Multiboot2 协议加载入内存,module2 会将 Linux 内核镜像加载到内存中,Hvisor 再将其移动到末尾的十六进制数字所指定的内存位置。

menuentry "Hvisor" {

multiboot2 /boot/hvisor # use multiboot spec to boot

module2 /boot/kernel/boot.bin 0

module2 /boot/kernel/boot.bin 5008000

module2 /boot/kernel/setup.bin 500a000

module2 /boot/kernel/vmlinux.bin 5100000

boot

}

最后,将 zone0 的根文件系统通过 sudo dd if=rootfs1.img的路径 of=/dev/sda2 bs=4M status=progress 指令写入 EXT4 分区。

NUC14 开机后,按 F10 进入 U 盘启动模式,选择 U 盘的 EFI 分区。(或者修改 BIOS 将 U 盘作为第一启动项)进入 GRUB 后,选择 Hvisor 即可。

五、有线网卡驱动问题

首先在 Linux 源码文件夹下执行 make modules 以生成 Module.symvers 文件。

Linux 镜像自带的 r8169 驱动可能无法在 NUC14 上运行,导致无法正常联网。因此需要下载 Realtek 官方提供的 r8125 驱动:Realtek PCIe FE / GbE / 2.5GbE / 5G / 10G Family Controller Software,下载 2.5G Ethernet LINUX driver r8125 for kernel up to x.xx 这一项。

下载完成后,进入 src 文件夹,执行 make -C linux所在路径 M=src所在路径 modules,将生成的 r8125.ko 内核模块放入 zone0 的根文件系统的特定位置,例如 /mnt/lib/modules/$(uname -r)/kernel/drivers/net/ethernet/realtek/,然后执行 depmod -a -b /mnt $(uname -r) 更新模块依赖索引。这样在进入 Hvisor 时,就可以执行 sudo modprobe r8125 加载网卡驱动了。

六、无线网卡驱动问题

如果要让 zone0 或 zone1 使用无线网卡,需要给内核添加如下配置项,重新编译:

# iwlwifi 无线网卡驱动

./scripts/config --module CONFIG_IWLWIFI

然后把内核模块安装到 /lib/modules/$(uname -r)。

make -j$(nproc)

make modules

make modules_install INSTALL_MOD_PATH=/path/to/rootfs

这里编译成内核模块,是因为无线网卡驱动在加载时可能需要从 Linux 文件系统中读取固件(firmware)文件。因此要等到文件系统准备完毕,才能进行驱动的初始化。编译成内核模块可以更好地控制驱动初始化的时机。

如果未在 Linux 文件系统中放置合适的固件文件,执行 sudo modprobe iwlwifi 后,可能会显示如下类型的报错。

Direct firmware load for iwlwifi-so-a0-gf-a0-73.ucode failed with error -2

Direct firmware load for iwlwifi-so-a0-gf-a0-72.ucode failed with error -2

Direct firmware load for iwlwifi-so-a0-gf-a0-71.ucode failed with error -2

...

从网上下载 iwlwifi 所需的固件文件,将其移动到 Linux 文件系统的 /lib/firmware 路径下。本示例所需的固件包括 iwlwifi-so-a0-gf-a0.pnvm 以及 iwlwifi-so-a0-gf-a0-72.ucode。

为 Linux 安装依赖:

sudo apt install wpasupplicant udhcpc

修改 init,添加如下内容:

modprobe iwlwifi

# wlan0 是无线网卡对应的接口

ip link set wlan0 up

# 连接 Wifi

wpa_passphrase "你的 Wifi 名称" "你的 Wifi 密码" > /etc/wpa_supplicant.conf

wpa_supplicant -B -i wlan0 -c /etc/wpa_supplicant.conf

# 获取 IP 地址

udhcpc -i wlan0

# 添加 DNS 解析服务器

echo "nameserver 114.114.114.114" > /etc/resolv.conf

echo "nameserver 8.8.8.8" >> /etc/resolv.conf

在NXP-IMX8MP上启动hvisor

1. 下载厂商提供的linux源码

https://pan.baidu.com/s/1XimrhPBQIG5edY4tPN9_pw?pwd=kdtk

提取码:kdtk

进入Linux/源码/目录下,下载OK8MP-linux-sdk.tar.bz2.0*3个压缩包,下载完成后,执行:

cd Linux/sources

# 合并分卷压缩包

cat OK8MP-linux-sdk.tar.bz2.0* > OK8MP-linux-sdk.tar.bz2

# 解压合并的压缩包

tar -xvjf OK8MP-linux-sdk.tar.bz2

解压后,OK8MP-linux-kernel目录就是linux源码目录。

2. linux源码编译

安装交叉编译工具

-

下载交叉编译工具链:

wget https://armkeil.blob.core.windows.net/developer/Files/downloads/gnu-a/10.3-2021.07/binrel/gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-gnu.tar.xz -

解压工具链:

tar xvf gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-gnu.tar.xz -

添加路径,使

aarch64-none-linux-gnu-*可以直接使用,修改~/.bashrc文件:echo 'export PATH=$PWD/gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-gnu/bin:$PATH' >> ~/.bashrc source ~/.bashrc

编译linux

-

切换到 Linux 内核源码目录:

cd Linux/sources/OK8MP-linux-sdk -

执行编译命令:

# 设置 Linux 内核配置 make OK8MP-C_defconfig ARCH=arm64 CROSS_COMPILE=aarch64-none-linux-gnu- # 编译 Linux 内核 make ARCH=arm64 CROSS_COMPILE=aarch64-none-linux-gnu- Image -j$(nproc) # 复制编译后的镜像到 tftp 目录 cp arch/arm64/boot/Image ~/tftp/

这里建立一个tftp目录,方便之后对镜像整理,也方便附录中使用tftp传输镜像。

3. 制作sd卡

-

将SD卡插入读卡器,并连接至主机。

-

切换至Linux/Images目录。

-

执行以下命令,进行分区:

fdisk <$DRIVE> d # 删除所有分区 n # 创建新分区 p # 选择主分区 1 # 分区编号为1 16384 # 起始扇区 t # 更改分区类型 83 # 选择Linux文件系统(ext4) w # 保存并退出 -

将启动文件写入SD卡启动盘:

dd if=imx-boot_4G.bin of=<$DRIVE> bs=1K seek=32 conv=fsync -

格式化SD卡启动盘的第一个分区为ext4格式:

mkfs.ext4 <$DRIVE>1 -

将SD卡读卡器拔出,重新连接。将根文件系统rootfs.tar解压到SD卡1号分区,rootfs.tar可以自行参考qemu-aarch64制作,也可以使用下面的镜像。

tar -xvf rootfs.tar -C <path/to/mounted/SD/card/partition>

rootfs.tar下载地址:

https://disk.pku.edu.cn/link/AADFFFE8F568DE4E73BE24F5AED54B00EB

文件名:rootfs.tar

- 完成后,弹出SD卡。

4. 编译hvisor

- 整理配置文件

将配置文件放到该放的地方,配置文件样例可以参考这里。

- 编译hvisor

进入hvisor目录,切换到main分支或dev分支,执行编译命令:

make ARCH=aarch64 FEATURES=platform_imx8mp,gicv3 LOG=info all

# 将编译后的hvisor镜像放入tftp

make cp

5. 启动hvisor和root linux

启动NXP板子之前,需要将tftp目录下的文件放到sd卡,比如放到sd卡的/home/arm64目录下,tftp目录下的文件包括:

- Image:root linux镜像,也可以用作non root linux镜像

- linux1.dtb, linux2.dtb:root linux和non root linux的设备树

- hvisor.bin:hvisor镜像

- OK8MP-C.dtb:这个用于uboot启动时做一些检查,本质没什么用,可以从这里获取OK8MP-C.dts

启动NXP板子:

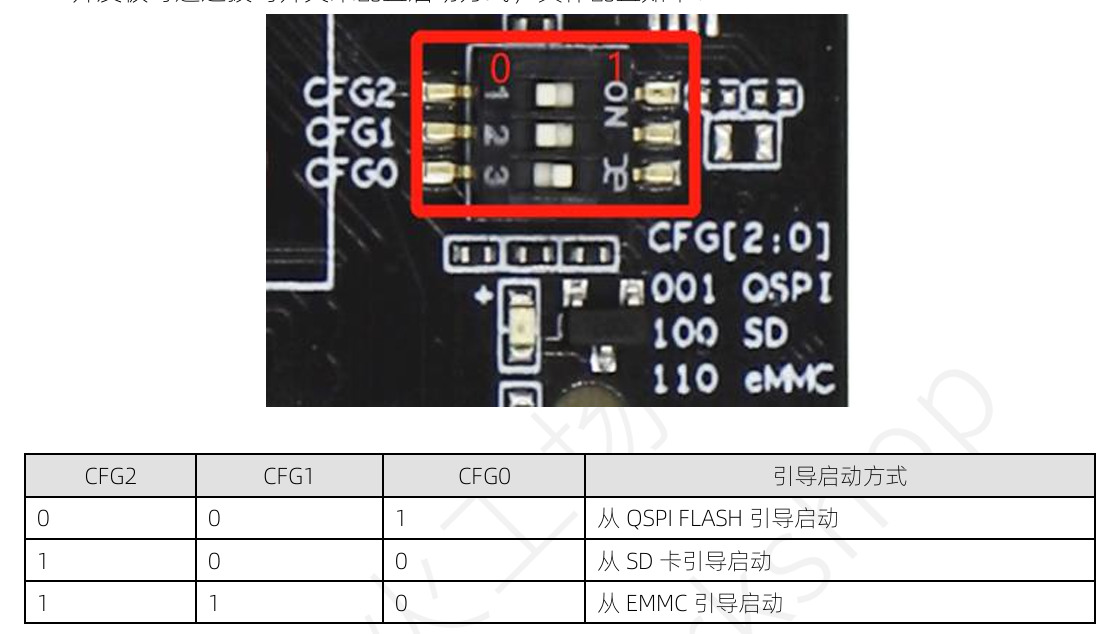

- 调整拨码开关以启用SD卡启动模式:(1,2,3,4) = (ON,ON,OFF,OFF)。

- 将SD卡插入SD插槽。

- 使用串口线将开发板与主机相连。

- 通过终端软件打开串口

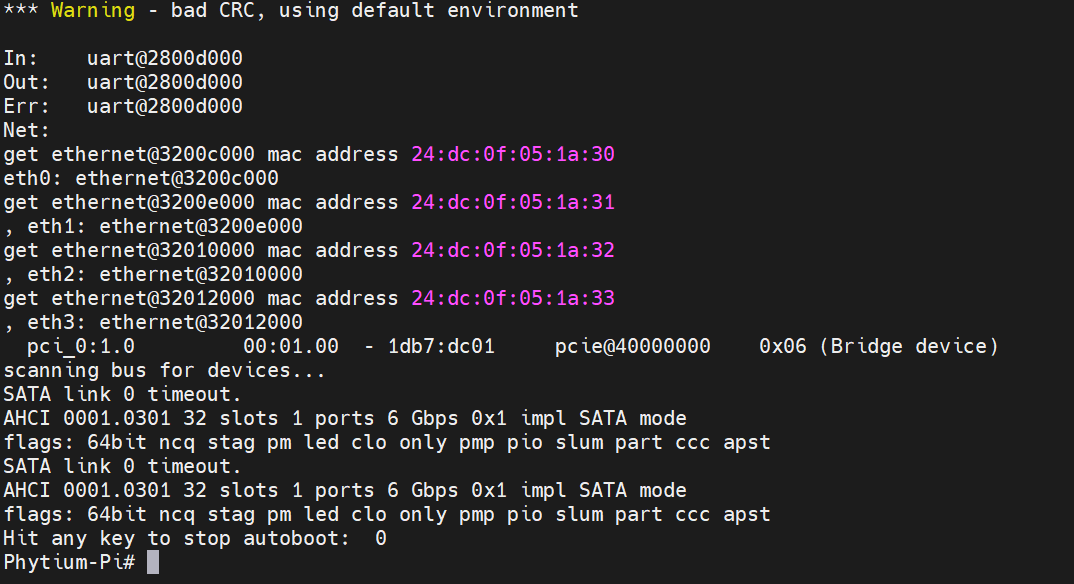

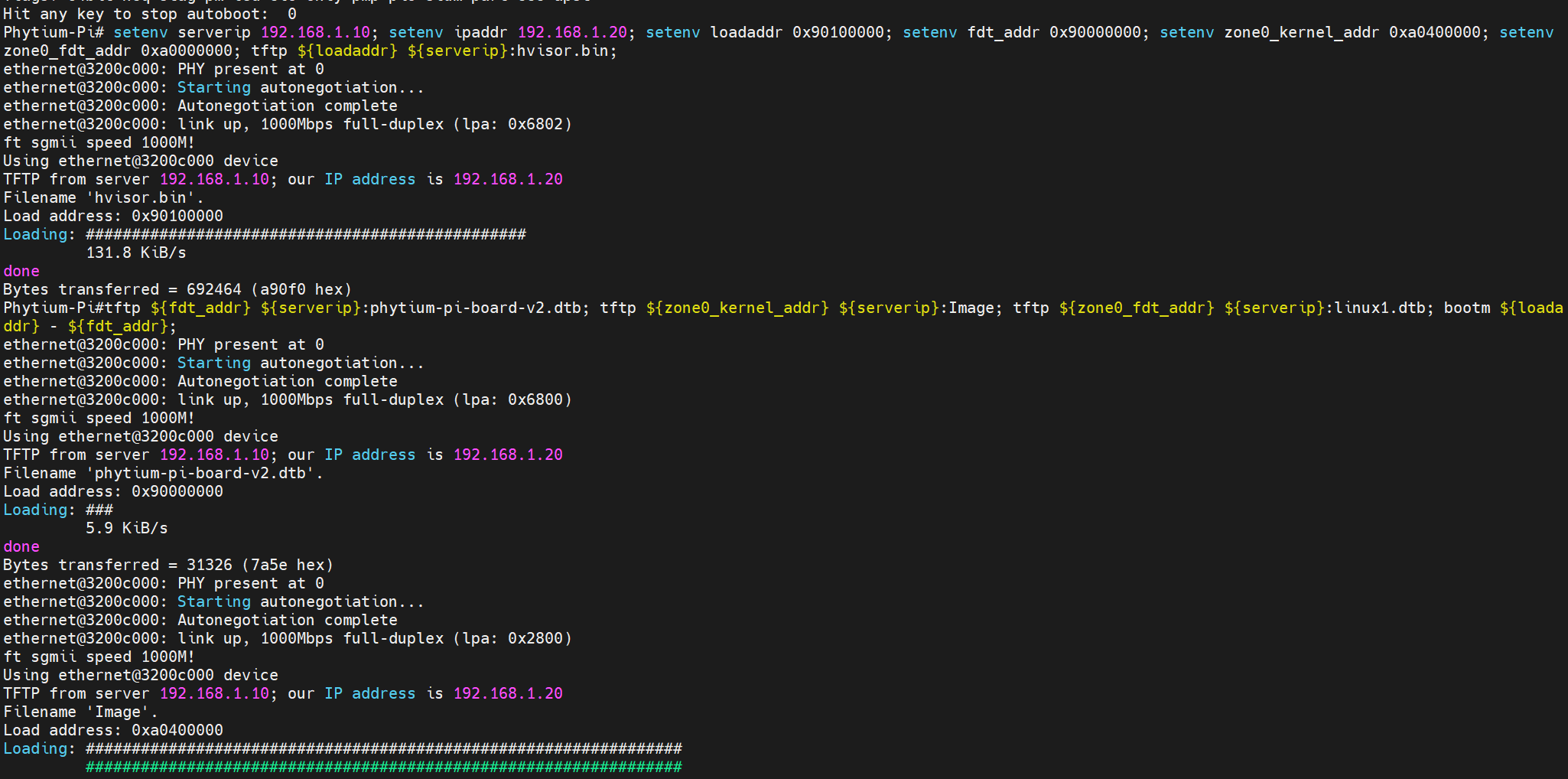

启动NXP板子后,串口应该有输出,重启开发板,立刻按下空格保持不懂,使uboot进入命令行终端,执行如下命令:

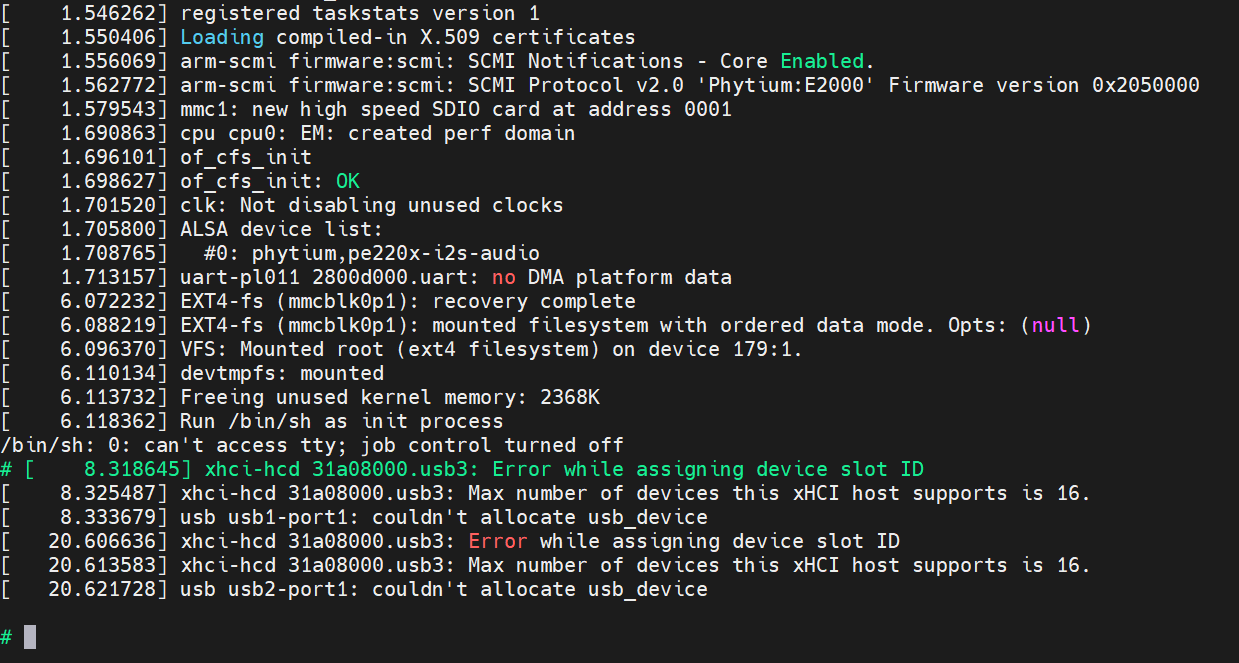

setenv loadaddr 0x40400000; setenv fdt_addr 0x40000000; setenv zone0_kernel_addr 0xa0400000; setenv zone0_fdt_addr 0xa0000000; ext4load mmc 1:1 ${loadaddr} /home/arm64/hvisor.bin; ext4load mmc 1:1 ${fdt_addr} /home/arm64/OK8MP-C.dtb; ext4load mmc 1:1 ${zone0_kernel_addr} /home/arm64/Image; ext4load mmc 1:1 ${zone0_fdt_addr} /home/arm64/linux1.dtb; bootm ${loadaddr} - ${fdt_addr};

执行后,hvisor应该就启动并自动进入root linux了。

6. 启动non root linux

启动non root linux需要用到hvisor-tool。具体请参考hvisor-tool的 README。

附. 使用tftp便捷传输镜像

tftp方便开发板与主机间的数据传输,不需要每次插拔sd卡。具体步骤如下:

对于ubuntu系统

如果你使用的是ubuntu系统,则依次执行:

-

安装 TFTP 服务器软件包

sudo apt-get update sudo apt-get install tftpd-hpa tftp-hpa -

配置 TFTP 服务器

创建 TFTP 根目录并设置权限:

mkdir -p ~/tftp sudo chown -R $USER:$USER ~/tftp sudo chmod -R 755 ~/tftp编辑 tftpd-hpa 配置文件:

sudo nano /etc/default/tftpd-hpa修改如下:

# /etc/default/tftpd-hpa TFTP_USERNAME="tftp" TFTP_DIRECTORY="/home/<your-username>/tftp" TFTP_ADDRESS=":69" TFTP_OPTIONS="-l -c -s"将

<your-username>替换为实际用户名。 -

启动/重启 TFTP 服务

sudo systemctl restart tftpd-hpa -

验证 TFTP 服务器

echo "TFTP Server Test" > ~/tftp/testfile.txttftp localhost tftp> get testfile.txt tftp> quit cat testfile.txt若显示 "TFTP Server Test",则 TFTP 服务器工作正常。

-

配置开机启动:

sudo systemctl enable tftpd-hpa -

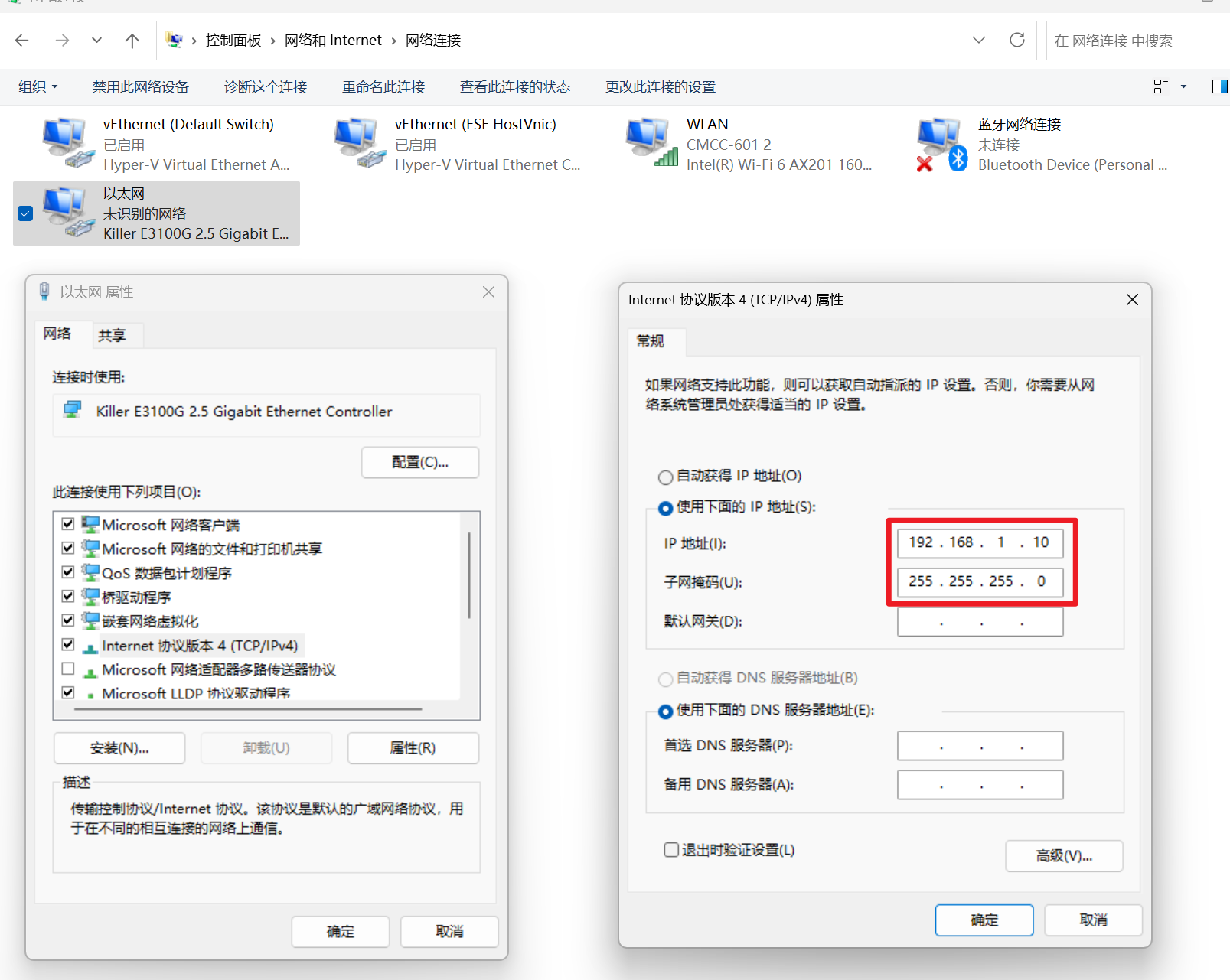

使用网线将开发板的网口(共有两个,请选择下方的一个)与主机连接。并配置主机有线网卡,ip:192.169.137.2, netmask: 255.255.255.0。

之后启动开发板,进入uboot命令行后,执行命令变为:

setenv serverip 192.169.137.2; setenv ipaddr 192.169.137.3; setenv loadaddr 0x40400000; setenv fdt_addr 0x40000000; setenv zone0_kernel_addr 0xa0400000; setenv zone0_fdt_addr 0xa0000000; tftp ${loadaddr} ${serverip}:hvisor.bin; tftp ${fdt_addr} ${serverip}:OK8MP-C.dtb; tftp ${zone0_kernel_addr} ${serverip}:Image; tftp ${zone0_fdt_addr} ${serverip}:linux1.dtb; bootm ${loadaddr} - ${fdt_addr};

解释:

setenv serverip 192.169.137.2:设置tftp服务器的IP地址。setenv ipaddr 192.169.137.3:设置开发板的IP地址。setenv loadaddr 0x40400000:设置hvisor镜像的加载地址。setenv fdt_addr 0x40000000:设置设备树文件的加载地址。setenv zone0_kernel_addr 0xa0400000:设置guest Linux镜像的加载地址。setenv zone0_fdt_addr 0xa0000000:设置root Linux的设备树文件的加载地址。tftp ${loadaddr} ${serverip}:hvisor.bin:从tftp服务器下载hvisor镜像到hvisor的加载地址。tftp ${fdt_addr} ${serverip}:OK8MP-C.dtb:从tftp服务器下载设备树文件到设备树文件的加载地址。tftp ${zone0_kernel_addr} ${serverip}:Image:从tftp服务器下载guest Linux镜像到guest Linux镜像的加载地址。tftp ${zone0_fdt_addr} ${serverip}:linux1.dtb:从tftp服务器下载root Linux的设备树文件到root Linux的设备树文件的加载地址。bootm ${loadaddr} - ${fdt_addr}:启动hvisor,加载hvisor镜像和设备树文件。

对于windows系统

可以参考这篇文章: https://blog.csdn.net/qq_52192220/article/details/142693036

此目录主要与 ZCU102 相关,介绍如下:

- 如何使用 Qemu 仿真 Xilinx ZynqMP ZCU102

- 如何在 Qemu ZCU102 和 ZCU102 实体开发板上启动 hvisor root linux 和 nonroot linux。

Qemu ZCU102 hvisor 启动

安装 Petalinux

- 安装 Petalinux 2024.1 请注意,本文以 2024.1 为例进行介绍,并不意味着其他版本不可以,只是其他版本未经验证,且测试中发现 Petalinux 对于操作系统有较强的依赖,请安装适合于自己操作系统的对应版本的 Petalinux.

- 将下载好的

petalinux.run文件放置到想要安装到的目录下,为其添加执行权限,之后直接./petalinux.run运行安装程序。 - 安装程序会自动检测所需要的环境,如果不符合则会将缺失的环境提示出来,只需要对其一个个

apt insntall即可。 - 安装完成后每次使用 Petalinux 前需要进入安装目录,手动

source settings.sh来添加环境变量,嫌麻烦将可以将该命令加入到~/.bashrc中

安装 ZCU102 BSP

- 下载对应于 Petalinux 版本的 BSP,例子中是 ZCU102 BSP 2024.1

- 激活 Petalinux 环境,即在 Petalinux 安装目录中

source settings.sh。 - 基于 BSP 创建 Petalinux Project:

petalinux-create -t project -s xilinx-zcu102-v2024.1-05230256.bsp - 此时会创建一个

xilinx-zcu102-2024.1文件夹,其中就有了 QEMU 模拟 ZCU102 所需的参数(设备树),以及预先编译好可以直接上板的 Linux 镜像、设备树、Uboot等。

编译 Hvisor

参照《在 Qemu 上运行 Hvisor》对编译 Hvisor 所需的环境进行配置,之后在 hvisor 目录下,执行:

make ARCH=aarch64 LOG=info BOARD=zcu102 cp

进行编译工作,目录下/target/aarch64-unknown-none(可能不同)/debug/hvisor,即为所需求的 hvisor 镜像。

准备设备树

使用现有设备树

在 Hvisor 的 image/devicetree 目录下,有 zcu102-root-aarch64.dts,其为已经经过测试用来启动RootLinux的设备树文件,对其进行编译即可。

dtc -I dts -O dtb -o zcu102-root-aarch64.dtb zcu102-root-aarch64.dts

如果 dtc 命令无效,则安装 device-tree-compiler。

sudo apt-get install device-tree-compiler

自行准备设备树

如果对设备有定制需求,则建议自行准备设备树,可以反编译 ZCU102 BSP 中的 pre-built/linux/images/system.dtb 获取完整设备树,基于 zcu102-root-aarch64.dts 进行增减。

准备镜像

使用现有镜像

建议直接使用 ZCU102 BSP 中的 pre-built/linux/images/Image 作为 Linux 内核在 ZCU102 上启动,其驱动配置完整。

自行编译

经过测试,linux 源码中 5.15 之前对于 ZYNQMP 的支持不全面,不建议自行编译时使用这之前的版本进行编译,在之后的版本进行编译时可以直接按照一般编译流程进行编译,因为源码对于 ZYNQMP 的基本支持默认开启。具体编译操作如下:

- 访问 linux-xlnx 官网下载 Linux 源码,下载时最好下载

zynqmp-soc-for-v6.3。 tar -xvf zynqmp-soc-for-v6.3解压源码- 进入解压好的目录,执行下述命令使用默认配置,

make ARCH=arm64 CROSS_COMPILE=aarch64-linux-gnu- defconfig - 进行编译:

make ARCH=arm64 CROSS_COMPILE=aarch64-linux-gnu- Image -j$(nproc) - 编译完成后,目录中

arch/arm64/boot/Image即为所需镜像。

启用 QEMU 仿真

- 激活 Petalinux 环境,即在Petalinux 安装目录中

source settings.sh。 - 进入

xilinx-zcu102-2024.1文件夹,使用下述命令即可在 QEMU仿真的 ZCU102上启动 hvisor,其中的文件路径需要按照自己的实际情况进行修改。

# QEMU 参数传递

petalinux-boot --qemu --prebuilt 2 --qemu-args '-device loader,file=hvisor,addr=0x40400000,force-raw=on -device loader,

file=zcu102-root-aarch64.dtb,addr=0x40000000,force-raw=on -device loader,file=zcu102-root-aarch64.dtb,addr=0x04000000,

force-raw=on -device loader,file=/home/hangqi-ren/Image,addr=0x00200000,force-raw=on -drive if=sd,format=raw,index=1,

file=rootfs.ext4'

# 启动 hvisor

bootm 0x40400000 - 0x40000000

Board ZCU102 hvisor 多模式启动

在 ZCU102 开发板 SD mode 下启动 Hvisor

准备 SD 卡

- 准备一块标准 SD 卡,对其进行分区,一块为 Boot 分区(FAT32),其余为文件系统分区(EXT4),windows 分区可以使用 DiskGenius,Linux 分区可以使用 fdisk、mkfs

- 准备一个文件系统,将其内容拷贝到任一文件系统分区中,可以参考 《NXPIMX8》 制作 Ubuntu 文件系统、也可以直接使用 ZCU102 BSP 中的文件系统。

- 将

zcu102-root-aarch64.dtb、Image、hvisor拷贝到 Boot 分区中。 - 在 SD mode 下,需要提供从 SD卡中提供 ATF、Uboot,因此将 ZCU102 BSP 中

pre-built/linux/images/boot.scr 和 BOOT.BIN拷贝到 BOOT 分区中。

启动 ZCU102

- 将 ZCU102 设置为 SD mode,插入 SD 卡,连接串口,上电

- 输入任意按键打断 Uboot 自动脚本执行,运行下述命令启动 hvisor 及 root linux:

fatload mmc 0:1 0x40400000 hvisor;fatload mmc 0:1 0x40000000 zcu102-root-aarch64.dtb

fatload mmc 0:1 0x04000000 zcu102-root-aarch64.dtb;fatload mmc 0:1 0x00200000 Image;bootm 0x40400000 - 0x40000000

- 如果成功启动,将可以在串口看到 hvisor 信息以及 linux 信息,最终进入文件系统。

在 ZCU102 开发板 Jtag mode 下启动 Hvisor

首先将板子附带的两个线缆连接到板子的 JTAG 和 UART 接口上,另一端通过 USB 连接到 PC。

然后在命令行打开一个 petalinux 工程,确保工程已经编译过并生成了对应的启动文件(vmlinux、BOOT.BIN等),之后进入工程根目录运行 [1]:

petalinux-boot --jtag --prebuilt 2

其中 prebuilt 代表启动的层次:

- Level 1: 只下载 FPGA bitstream,启动 FSBL 和 PMUFW

- Level 2: 下载 FPGA bitstream 并启动 UBOOT,并启动 FSBL、PMUFW 和 TF-A(Trusted Firmware-A [2])

- Level 3: 下载并启动 linux,并加载或启动 FPGA bitstream、FSBL、PMUFW、TF-A、UBOOT

之后 JTAG 会通过 JTAG 线把对应的文件下载到板子上(保存到指的内存地址),并启动对应的 bootloader,具体官方的 UBOOT 默认脚本参见工程镜像目录的 boot.scr 文件。

由于 hvisor 需要单独的 UBOOT 命令和自制的 fitImage 启动,请参考 UBOOT FIT 镜像制作、加载与启动。

制作好 fitImage 后,请替换 petalinux images生成目录内的文件(Image.ub),使得 JTAG 加载我们自己制作的 fitImage 到 petalinux 工程配置好的默认 FIT 镜像加载地址,这样 JTAG 启动时会将我们的 fitImage 通过 JTAG 线加载到板子内存对应的地址中,之后再通过 uboot 命令行 extract 和 bootm。

另一个 UART 线可用于以观察 ZCU102 板子的输出(包括 FSBL、UBOOT、linux 等输出),可以通过 screen / gtkterm / termius / minicom 等串口工具查看。

请注意

由于 petalinux 规定了一些固定内存地址,如 linux kernel、fitImage、DTB 的默认加载地址(可在 petalinux 编译工程时配置),由于我们需要加载启动自制的 fitImage,目前发现的问题是如果 root linux dtb 在 its 中所写的加载地址和 petalinux 编译时的加载地址一致,会导致该 dtb 被覆盖为默认的 petalinux dtb,从而导致root linux接受到错误的 dtb 而无法启动。因此需要在编译时指定和 petalinux 默认 dtb/fitImage 加载地址不同的地址,以防止出现其他问题。

参考文献

[1] PetaLinux Tools Documentation: Reference Guide (UG1144).https://docs.amd.com/r/2023.1-English/ug1144-petalinux-tools-reference-guide/Booting-a-PetaLinux-Image-on-Hardware-with-JTAG [2] Trusted Firmware-A Documentation.https://trustedfirmware-a.readthedocs.io/en/latest/

ZCU102 NonRoot 启动

- 使用启动 Root 时所用的 Linux 内核源码编译 hvisor-tool,详细编译流程可以参考 Readme.

- 准备启动 NonRoot 所需要的

virtio_cfg.json和zone1_linux.json,这里可以直接使用 hvisor-tool 目录下的example/zcu102-aarch64,里面的内容已经经过验证,确保可以启动。 - 准备 NonRoot 所需要的 linux 内核 Image,文件系统 rootfs,以及设备树 linux1.dtb。其中的内核和文件系统可以和 Root 一样,Linux1.dtb 则是按需配置,也可以使用 hvisor 目录下的

images/aarch64/devicetree/zcu102-nonroot-aarch64.dts. - 将

hvisor.ko, hvisor, virtio_cfg, zone1_linux.json, linux1.dtb, Image, rootfs.ext4拷贝到 Root Linux 所用的文件系统中。 - 在 RootLinux 输入下述命令启动 NonRoot:

# 加载内核模块

insmod hvisor.ko

# 创建 virtio 设备

nohup ./hvisor virtio start virtio_cfg.json &

# 根据 json 配置文件启动 NonRoot

./hvisor zone start zone1_linux.json

# 查看 NonRoot 的输出,并交互。

screen /dev/pts/0

更多操作细节参考 hvisor-tool Readme

UBOOT FIT 镜像制作、加载与启动

本文介绍 FIT 镜像相关的基本知识,以及如何制作、加载和启动 FIT 镜像。

ITS 源文件

ITS 是 uboot 生成 FIT 镜像(FIT Image)的源码,即 Image Tree Source,其采用 Device Tree Source(DTS)语法格式,可以通过 uboot 提供的工具 mkimage 生成 FIT 镜像。

在 hvisor 的 ZCU102 移植中,使用 FIT 镜像打包 hvisor、root linux、root dtb 等文件到一个 fitImage 中,便于在 QEMU 和实际硬件上启动。

用于 ZCU102 平台的 ITS 文件位于 scripts/zcu102-aarch64-fit.its:

/dts-v1/;

/ {

description = "FIT image for HVISOR with Linux kernel, root filesystem, and DTB";

images {

root_linux {

description = "Linux kernel";

data = /incbin/("__ROOT_LINUX_IMAGE__");

type = "kernel";

arch = "arm64";

os = "linux";

...

};

...

root_dtb {

description = "Device Tree Blob";

data = /incbin/("__ROOT_LINUX_DTB__");

type = "flat_dt";

...

};

hvisor {

description = "Hypervisor";

data = /incbin/("__HVISOR_TMP_PATH__");

type = "kernel";

arch = "arm64";

...

};

};

configurations {

default = "config@1";

config@1 {

description = "default";

kernel = "hvisor";

fdt = "root_dtb";

};

};

};

其中,__ROOT_LINUX_IMAGE__、__ROOT_LINUX_DTB__、__HVISOR_TMP_PATH__将通过 Makefile 内的 sed 命令替换为实际的路径。在 its 源码中,主要分为 images 和 configurations 两个部分,images 部分定义了要打包的文件,configurations 部分定义了如何组合这些文件,在 UBOOT 启动时,会根据 configurations 中的 default 配置自动加载对应的文件到指定的地址,并且可以通过设置多个 configurations 来支持启动时选择加载不同配置的镜像。

Makefile 中 mkimage 对应的命令:

.PHONY: gen-fit

gen-fit: $(hvisor_bin) dtb

@if [ ! -f scripts/zcu102-aarch64-fit.its ]; then \

echo "Error: ITS file scripts/zcu102-aarch64-fit.its not found."; \

exit 1; \

fi

$(OBJCOPY) $(hvisor_elf) --strip-all -O binary $(HVISOR_TMP_PATH)

# now we need to create the vmlinux.bin

$(GCC_OBJCOPY) $(ROOT_LINUX_IMAGE) --strip-all -O binary $(ROOT_LINUX_IMAGE_BIN)

@sed \

-e "s|__ROOT_LINUX_IMAGE__|$(ROOT_LINUX_IMAGE_BIN)|g" \

-e "s|__ROOT_LINUX_ROOTFS__|$(ROOT_LINUX_ROOTFS)|g" \

-e "s|__ROOT_LINUX_DTB__|$(ROOT_LINUX_DTB)|g" \

-e "s|__HVISOR_TMP_PATH__|$(HVISOR_TMP_PATH)|g" \

scripts/zcu102-aarch64-fit.its > temp-fit.its

@mkimage -f temp-fit.its $(TARGET_FIT_IMAGE)

@echo "Generated FIT image: $(TARGET_FIT_IMAGE)"

请注意

不要将已经由 UBOOT 打包的 Image 传入 its 源文件,否则会导致 二次打包!因为 its 中指向的文件应为原始文件(vmlinux 等),mkimage 在导入 its 时对逐个文件进行打包处理(vmlinux->"Image",然后内嵌到 fitImage)

在 petalinux qemu 中通过 FIT 镜像启动 hvisor 和 root linux

由于 fitImage 一个文件就包括了所有需要的文件,因此对于 qemu 来说只需要通过 loader 把这个文件加载到内存中一个合适的位置即可。

之后 qemu 启动并进入 UBOOT,可以使用下面的命令启动(具体的地址请根据实际情况修改,实际使用时可以把所有行写到一行内 copy 到 UBOOT 进行启动,也可以保存到环境变量 bootcmd 中,需要UBOOT挂载一个可持久化的 flash 用于环境变量保存):

setenv fit_addr 0x10000000; setenv root_linux_load 0x200000;

imxtract ${fit_addr} root_linux ${root_linux_load}; bootm ${fit_addr};

参考文献

[1] Flat Image Tree (FIT). https://docs.u-boot.org/en/stable/usage/fit/

新板子需要的操作

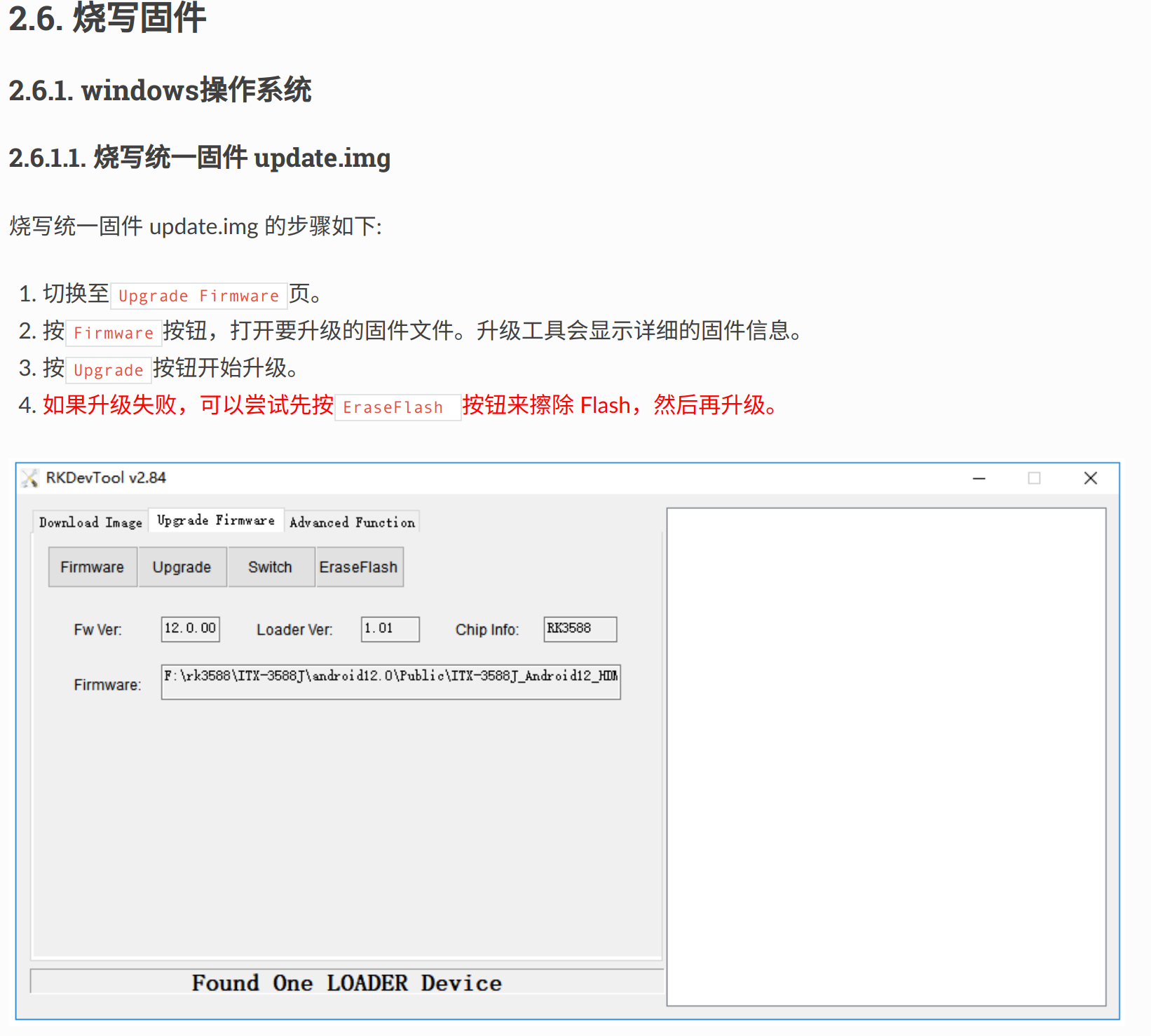

如果板子为新到手的 RK3588,则可能板子内部未被烧写任何内容,包括引导,因此需要首先对板子进行初步烧写,为其烧写 Uboot、Linux、Rootfs 等内容。烧写推荐在 Windows 通过RKDevTool完成。

可以直接下载此链接中的 update.img。此镜像打包了上述所有内容。直接烧写此镜像即可一步到位,具体操作如下:

- 用 USB 连接电脑和板子上的 Type-C 口。

- 首先让板子处于 MaskRoom 或者 Loader 模式(可以在 RKDevTool 识别到)

- Loader 模式:在通电状态下同时按住 RST 和 BOOT 按键,或者在 Uboot、Linux 下输入

reboot loader - MaskRoom 模式:新板子默认处于此模式。

- Loader 模式:在通电状态下同时按住 RST 和 BOOT 按键,或者在 Uboot、Linux 下输入

- 在 RKDevTool 中按照下图进行操作

获取 RK3588 内核镜像

RK3588 有着专用的内核镜像,源码可以通过此链接获取。

为了方便快速上手,这里的内核已经是经过编译的内核,因此文件较大。可以通过kernel/arch/arm64/boot/Image直接获取镜像,也可利用现成的.config 重新定制所需镜像。

当然,如果不关心内核源码,可以通过此链接直接获取 Image。

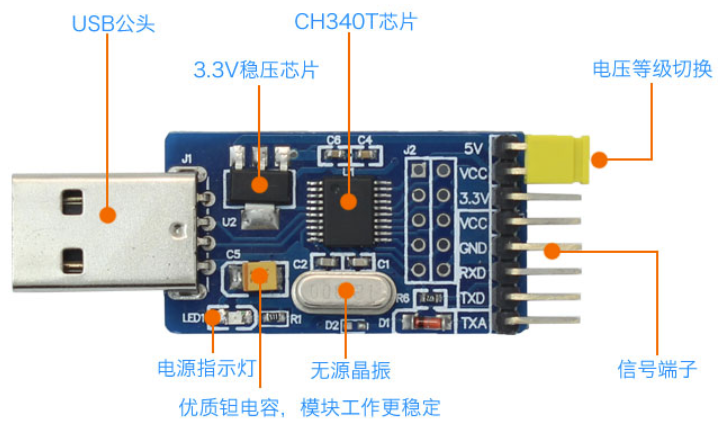

串口连接

RK3588 的串口比较特殊,需要自行购买 USB转TTL 转换器进行连接

连接时 RT-TX、TX-RD、GND-GND,连接到电脑后串口波特率为1500000。

重新烧写 Uboot

要想启动 hvisor,原有的 Uboot 没有等待时间,会直接启动 Linux。需要对 Uboot 进行重新烧写,这里也已经准备好了一份 Uboot 及其烧写工具,通过Uboot、Upgrade-tool即可获取。

在 Linux 系统下,同样用 Usb 连接板子和电脑,并使其处于 Loader 模式:

chmod +777 /path/to/upgrade_tool

sudo upgrade_tool di -u /path/to/uboot.img

编译 Hvisor 和设备树

- 和其他开发板类似,拉取 hvisor 最新代码,仓库地址:https://github.com/syswonder/hvisor。进入目录后编译 hvisor:

make BID=aarch64/rk3588 - 进入

/images/aarch64/devicetree/,rk3588-root-aarch64-sdmmc.dts是 RK3588 RootLinux 所使用的设备树,rk3588-nonroot-aarch64.dts是 RK3588 NonRootLinux 所使用的设备树。 可以使用下面的命令对其编译:dtc -I dts -O dtb rk3588-nonroot-aarch64.dts -o ./linux1.dtb dtc -I dts -O dtb rk3588-root-aarch64-sdmmc.dts -o ./zone0.dtb

制作文件系统

准备一个 SD 卡,分区两块,第一块 FAT32 格式,大小 1g;第二块 EXT4 格式。

下载文件系统,将此文件系统解压到 EXT4 格式分区下即可。

当然,也可以自行制作,参考基于ubuntu_base构建文件系统。

启动 RootLinux

TFTP

如果已经搭建了 TFTP 服务器,那么可以以方便的方式快速启动 RootLinux,具体而言:

- 将 Image、zone0.dtb、hvisor.bin 复制到 ~/tftp 文件夹下

- 用网线连接主机与开发板,配置主机ip为

192.168.137.2,子网掩码255.255.255.0。 - 直接开机并连接串口即可,uboot 将自动下载 tftp 文件夹下的内容并启动。

如果有搭建需求,可以参考嵌入式平台快速开发-Tftp 服务器搭建与配置。

无 TFTP

此时 SD 卡中第一块 FAT32 分区即派上了用场,将 Image、zone0.dtb、hvisor.bin 复制到此分区中

- 启动开发板,连接串口。

- 打断 Uboot 自动启动。

- 输入下述指令启动 RootLinux

fatload mmc 0:1 0x00480000 hvisor.bin;fatload mmc 0:1 0x10000000 zone0.dtb;fatload mmc 0:1 0x09400000 Image;bootm 0x00480000 - 0x10000000

启动 NonRootLinux

下载现成的配置文件

通过此链接可下载可用的 NonRoot 配置,包括 Image、配置文件、rootfs等,将其解压到 RootLinux 的文件系统中,其可以帮助快速启动Nonroot,主要启动的设备有virtio-blk和virtio-console,也可根据自己的需求直通设备。

Tips:

请不要随意修改 Image 为 Rootlinux 使用的 Image,此会导致 Nonroot 启动失败!

编译 hvisor-tool

拉取 Hvisor-tool 的最新代码:https://github.com/syswonder/hvisor-tool/tree/main,进行编译:

make all ARCH=aarch64 LOG=LOG_INFO KDIR=RK3588内核源码 VIRTIO_GPU=n

更多细节请参考 hvisor-tool 的 Readme.md。

注意,内核源码必须已经经过编译,否则hvisor-tool将会因为找不到编译产物而报错。

Tips:

编译 hvisor-tool 时所使用的 glibc 版本需要保证 Rootlinux 文件系统也支持,否则会导致 hvisor-tool 不能正常工作!

例如,本文给出的 Rootlinux Rootfs 为 Ubuntu 24.04。编译机的 Glibc 版本要不高于 Ubuntu24.04 的 Glibc 版本,这里由于 Ubuntu24.04 较新,一般是满足的。

当然,上述操作是通过对齐两个文件系统所用的 glibc 版本来完成的,也可以直接在 Rootlinux 文件系统中编译 hvisor-tool,或者在编译机指定 Rootlinux 的文件系统目录,使得编译链接时直接链接 Rootlinux 文件系统的 glibc,具体如下:

make all ARCH=aarch64 LOG=LOG_INFO KDIR=RK3588内核源码 VIRTIO_GPU=n \

ROOT=/path/to/target_rootfs

启动

在 Rootlinux 下执行下述命令

insmod hvisor.ko

nohup ./hvisor virtio start virtio_cfg.json &

./hvisor zone start zone1_linux.json

screen /dev/pts/0

即可看到第二个虚拟机(Nonroot)的输出。

Tips:

如果不按照上述流程配置 Rootlinux 的文件系统,或者随着版本迭代,可能会出现现成配置文件不可用的情况,此时需要自行更新配置,我们也会尽早跟进。

具体最新配置格式可以参考 hvisor-tool 下的 example 进行。

基于 RK3588 的 矽慧通 X3300 快速上手

本文档旨在为开发者详细介绍在 矽慧通 X3300 开发板上部署并启动 hvisor 的完整流程。

操作环境基于 Ubuntu 22.04 主机。我们假定已获取好 Rockchip Linux SDK 及 矽慧通 X3300 相应的配置文档 / 配置文件。文中所述的开发板特指基于 RK3588 的 矽慧通 X3300。

需要准备的器材

| 类别 | 器材名称 | 规格要求 | 数量 | 用途说明 |

|---|---|---|---|---|

| 核心设备 | 矽慧通 X3300 | 1 块 | 主要开发平台 | |

| 电源设备 | 电源适配器 | DC 9-36V | 1 个 | 供电 |

| 调试工具 | USB 转串口模块 | 支持 1.5 Mbps 波特率 | 1 个 | 串口调试和日志输出 |

| 连接线缆 | Type-C USB 线 | 数据线 | 1 条 | 连接 OTG 口用于烧录 |

| 网络设备 | 以太网线 | 标准网线 | 1 条 | 网络通信 |

| 显示设备 | HDMI 线 | 标准 HDMI 接口 | 1 条 | 连接显示器 |

| 主机环境 | Ubuntu 主机 | Ubuntu 22.04 系统 | 1 台 | 编译和烧录环境 |

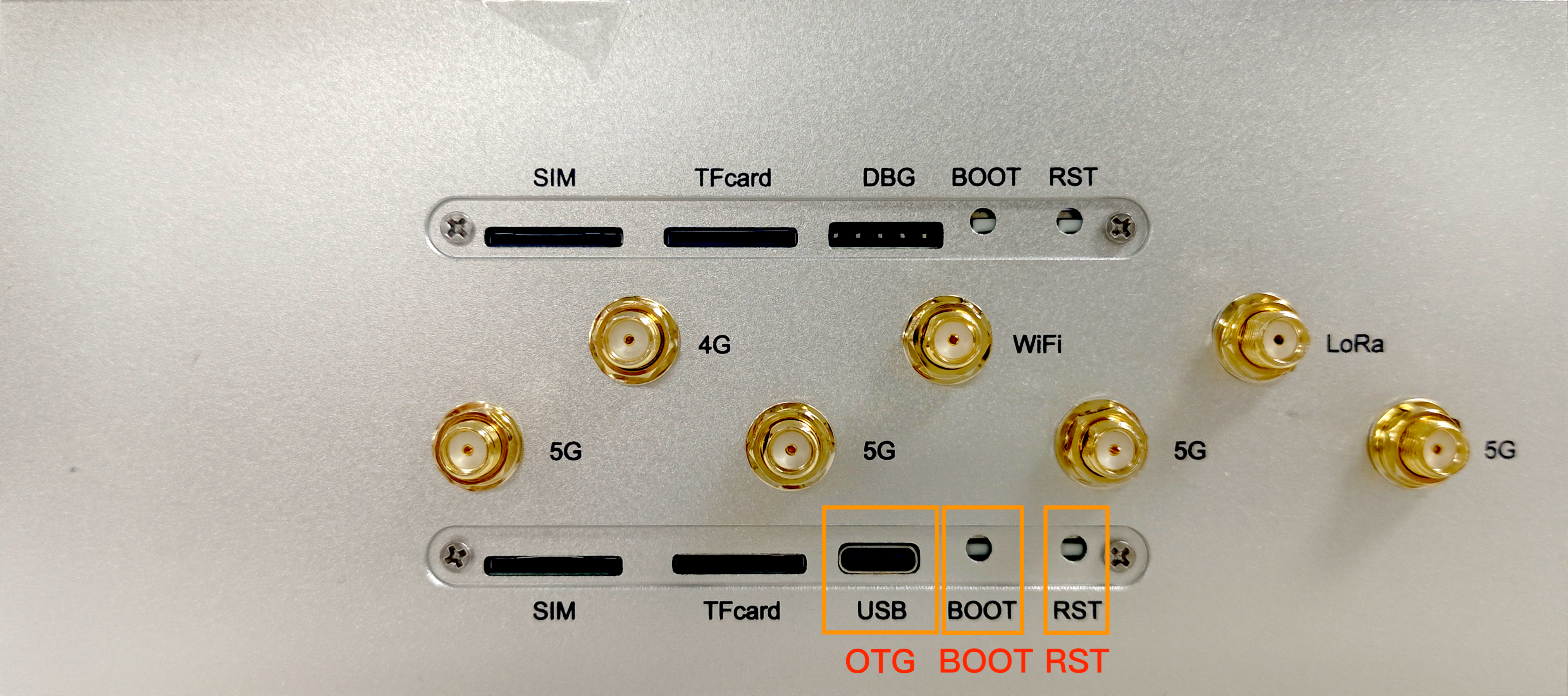

开发板介绍

在开始之前,请确保开发板已备妥,并熟悉其基本接口布局。

本文档操作所涉及的接口均位于开发板的前后两端。

上图所示为开发板前侧接口,需要用到的有:

- OTG 口:Type-C USB 接口,用于烧录。

- BOOT 和 RST 按钮:下层标识 BOOT 和 RST 的按钮,用于进入 MaskROM 模式和复位开发板。

上图所示为开发板后侧接口,需要用到的有:

- 电源:位于右侧,DC 9-36 V 接入,中间为正,两侧为负,可接入任意两个 V+ / V- 接线柱;

- 调试串口:下层右侧标识有 DEBUG 的 RXD、TXD;

- 以太网口:ETH1,设备树配置中为

ethernet@fe1c0000; - 图像输出 HDMI:设备树配置中为

hdmi@fde80000;

电源

请使用规格匹配的电源适配器连接至开发板的 DC 电源接口,以确保供电稳定。该开发板支持 9-36V 宽压输入。正确连接电源后,开发板后侧上下两层的电源指示灯 PWR 均应亮起,如下图所示。

串口连接

为进行设备调试与查看启动日志,需要通过 USB 转串口模块连接到开发板的调试串口。

默认串口参数如下:

| 参数项 | 参数值 |

|---|---|

| 波特率 (Baud Rate) | 1500000 |

| 数据位 (Data Bits) | 8 |

| 停止位 (Stop Bits) | 1 |

| 校验位 (Parity) | None |

硬件连接正确后,可使用 minicom 等串口工具进行通信。

# 如果未安装 minicom,先执行下面的命令安装

# sudo apt update && sudo apt install minicom

# 定义串口参数

BAUD_RATE=1500000

SERIAL_DEVICE="/dev/ttyUSB0"

# 启动 minicom

sudo minicom -b "${BAUD_RATE}" -D "${SERIAL_DEVICE}"

接线提示

- 标准接法(交叉连接):将模块的

RXD连接到开发板的TXD,TXD连接到RXD,GND连接GND。- 特殊情况(直连):部分厂商(如 Firefly)的模块可能已在内部做了交叉处理,此时需要

RXD接RXD,TXD接TXD。请务必参考模块说明书或咨询厂商以确认正确的接线方式。

进入 Loader / MaskROM 模式

开发者可通过以下方法,使开发板进入指定的烧录模式。

进入 MaskROM 模式

MaskROM 模式是芯片内置的底层启动模式,主要用于设备首次烧录或系统固件损坏时进行修复。

- 保持开发板处于通电状态。

- 同时按住

BOOT键与RST键。 - 先松开

RST键。 - 稍等片刻后,再松开

BOOT键,此时开发板即进入 MaskROM 模式。

进入 Loader 模式

Loader 模式通过软件命令进入,是常规固件升级时使用的标准模式。

- 在开发板已启动的系统 Linux / Android 或者 U-Boot 的终端中,执行以下命令:

reboot loader - 命令执行后,开发板将自动重启并进入 Loader 模式。

烧录基础系统

新出厂的开发板可能未预装任何固件。在这种情况下,需要首次烧录基础系统,包括 U-Boot、Linux 内核和根文件系统 (Rootfs),以便检验开发板是否正常工作。

编译固件

下面编译 Rockchip Linux SDK 以生成 update.img。

首先切换到 SDK 的目录,查看目录结构如下:

ROCKCHIP_LINUX_SDK_DIR="~/rockchip_linux_sdk"

cd "${ROCKCHIP_LINUX_SDK_DIR}"

tree -L 1

user@host:~/rockchip_linux_sdk$ tree -L 1

.

├── app

├── buildroot

├── build.sh -> device/rockchip/common/scripts/build.sh

├── debian

├── device

├── docs

├── external

├── kernel

├── Makefile -> device/rockchip/common/Makefile

├── output

├── prebuilts

├── README.md -> device/rockchip/common/README.md

├── rk3588_linux_release.xml

├── rkbin

├── rkflash.sh -> device/rockchip/common/scripts/rkflash.sh

├── rockdev -> output/firmware

├── tools

├── u-boot

├── uefi

└── yocto

在编译开始之前,需要修改 U-Boot 的配置,以将自动启动延迟从 0 调整为 10 秒,方便 U-Boot 启动 Debian 之前按下 Ctrl + C 停止启动。

sed -i 's/CONFIG_BOOTDELAY=0/CONFIG_BOOTDELAY=10/g' u-boot/configs/rk3588_defconfig

下面开始编译。通过环境变量 RK_ROOTFS_SYSTEM 指定编译的根文件系统类型为 Debian,然后调用 build.sh 即可即可开始编译。

export RK_ROOTFS_SYSTEM="debian"

./build.sh sysoul_x3300_defconfig && ./build.sh

编译结果为 output/update/Image/update.img。

配置烧录工具

Rockchip 在 Linux 平台下使用 upgrade_tool 进行烧录,编译完成之后,upgrade_tool 将位于 tools/linux/Linux_Upgrade_Tool/ 目录下。

当然,也可以直接从 GitHub 仓库中下载。

# 安装依赖

sudo apt update && sudo apt install libudev-dev libusb-1.0-0-dev

# 克隆包含烧录工具的仓库

git clone https://github.com/vicharak-in/Linux_Upgrade_Tool.git

# 将工具路径添加到 PATH 环境变量,并使其立即生效

echo 'export PATH="$PATH:'$(pwd)/Linux_Upgrade_Tool'"' >> ~/.bashrc

source ~/.bashrc

连接设备并进入 MaskROM 模式

对于一块全新的开发板,我们需要手动使其进入 MaskROM 模式。

- 请按照前述步骤,使开发板进入 MaskROM 模式。

- 使用 USB 线缆将开发板的 USB-OTG 口连接到主机。

- 执行以下命令,检查设备是否被正确识别:

sudo upgrade_tool ld # ListDevice,查看设备

如果看到类似如下的输出,说明设备已准备就绪。

List of rockusb connected(1)

DevNo=1 Vid=0x2207,Pid=0x350b,LocationID=322 Mode=Maskrom SerialNo=

注意:

Vid=0x2207是 Rockchip 公司的 USB 厂商 ID。如果未检测到设备,请检查 USB 线缆连接或更换主机的 USB 端口。

烧录固件

接下来,使用 upgrade_tool 工具将 update.img 固件包烧录至开发板的闪存。

sudo upgrade_tool uf update.img -noreset # UpgradeFirmware,更新固件,使用 -noreset 参数防止烧录后自动重启,便于我们手动控制

烧录过程将持续数分钟,终端会显示详细的进度日志。

Loading firmware...

Support Type:3588 FW Ver:<FW-Ver> FW Time:<YYYY-MM-DD hh:mm:ss>

Loader ver:<Loader-ver> Loader Time:<YYYY-MM-DD hh:mm:ss>

Start to upgrade firmware...

Download Boot Start

Download Boot Success

Wait For Maskrom Start

Wait For Maskrom Success

Test Device Start

Test Device Success

Check Chip Start

Check Chip Success

Get FlashInfo Start

Get FlashInfo Success

Prepare IDB Start

Prepare IDB Success

Download IDB Start

Download IDB Success

Download Firmware Start

Download Image... (100%)

Download Firmware Success

Upgrade firmware ok.

当看到 Upgrade firmware ok. 消息时,表示烧录成功。

重启并验证

烧录完成后,手动重启开发板以加载新系统。

sudo upgrade_tool rd # ResetDevice,复位设备

终端应返回:

Reset Device OK.

此时,开发板将启动预装的 Debian 系统。可以将 HDMI 连接到显示器,稍等片刻即可看到图形化界面。

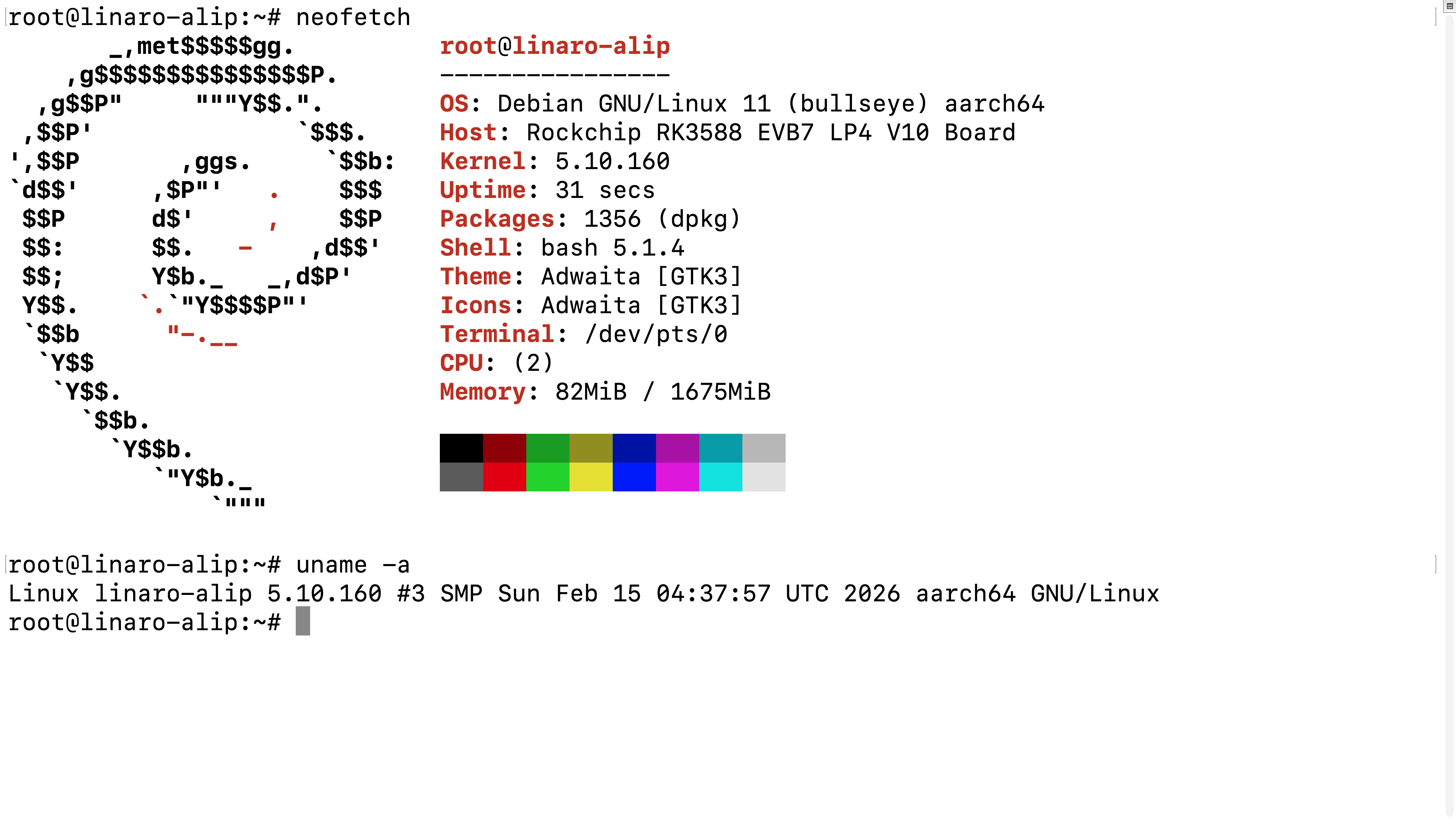

同时,在串口终端中也能观察到完整的启动日志以及控制台。

root@linaro-alip:/#

启动 hvisor

后续主机和开发板之间的文件传输均通过 IPv4 网络和 TFTP 协议进行。

配置主机网络并搭建 TFTP 服务器

首先配置主机的 IPv4 网络。我们将主机与开发板配置在一个点对点的 /30 网络中,该网络仅包含两个可用的主机地址,适用于这种直连场景。

HOST_NET_DEVICE="enp49s0" # 请根据实际情况修改为主机的网卡名称

HOST_IPV4="192.168.255.1"

NETMASK="255.255.255.252" # /30 子网掩码

sudo ifconfig "${HOST_NET_DEVICE}" "${HOST_IPV4}" netmask "${NETMASK}"

在主机上同时安装 TFTP 服务器软件和 TFTP 客户端软件(用于测试服务器是否正常工作)。

sudo apt update && sudo apt install tftpd-hpa tftp-hpa

创建 TFTP 根目录并设置权限。

TFTP_DIR="/srv/tftp"

sudo mkdir -p "${TFTP_DIR}"

sudo chown tftp:tftp "${TFTP_DIR}"

sudo chmod -R ugo+rw,a+X "${TFTP_DIR}"

编辑 tftpd-hpa 配置文件。

sudo tee /etc/default/tftpd-hpa > /dev/null <<EOF

# /etc/default/tftpd-hpa

TFTP_USERNAME="tftp"

TFTP_DIRECTORY="/srv/tftp"

TFTP_ADDRESS=":69"

TFTP_OPTIONS="-l -c -s"

EOF

启动 TFTP 服务器。

sudo systemctl start tftpd-hpa.service

测试 TFTP 服务器是否正常工作。

TFTP_DIR="/srv/tftp"

TEST_SRC_FILE_NAME="testfile.txt"

TEST_DST_FILE_NAME="downloaded_testfile.txt"

echo "TFTP Automation Test" > "${TFTP_DIR}/${TEST_SRC_FILE_NAME}" && \

tftp localhost -c get "${TEST_SRC_FILE_NAME}" "${TEST_DST_FILE_NAME}" && \

diff -q "${TFTP_DIR}/${TEST_SRC_FILE_NAME}" "${TEST_DST_FILE_NAME}" && \

echo "TFTP Test PASSED" || echo "TFTP Test FAILED" ; \

rm -f "${TFTP_DIR}/${TEST_SRC_FILE_NAME}" "${TEST_DST_FILE_NAME}"

准备 root-linux

提取 kernel

可以直接将原有 Rockchip Linux SDK 的编译结果中的 kernel(位于 kernel/arch/arm64/boot/ 路径下)提取出来,复制到 TFTP 目录。

TFTP_DIR="/srv/tftp"

ROCKCHIP_LINUX_SDK_DIR="$HOME/rockchip_linux_sdk"

cp "${ROCKCHIP_LINUX_SDK_DIR}/kernel/arch/arm64/boot/Image" "${TFTP_DIR}"

编译 device-tree

将开发板的 dts (例如 sysoul_x3300.dts) 复制一份,命名为 zone0.dts,并进行以下修改以划分资源给 GuestOS:

-

为 GuestOS 预留 CPU 核心: hvisor 的设计中,root-linux 和 GuestOS 各使用一部分 CPU 核心。此处我们仅为 root-linux 保留

cpu0和cpu1。在设备树中找到其余的cpu节点,将其删去。 -

为 hvisor 和 GuestOS 预留内存空间: 在

memory节点的reserved-memory区域下,添加两块保留内存。一块用于 hvisor 本身,另一块用于 GuestOS 的物理内存。no-map属性确保 root-linux 内核不会映射和使用这些区域。

--- a/sysoul_x3300.dts

+++ b/zone0.dts

...

reserved-memory {

...

+

+ hvisor@480000 {

+ no-map;

+ reg = <0x00 0x480000 0x00 0x400000>;

+ };

+

+ nonroot@50000000 {

+ no-map;

+ reg = <0x00 0x50000000 0x00 0x25000000>;

+ };

};

...

- 添加 hvisor virtio 设备节点:

在根节点下添加一个设备节点,用于 hvisor 的 virtio 后端驱动与 root-linux 内核进行通信。中断号需要根据具体的硬件平台进行配置,此处配置为

0x20。

--- a/sysoul_x3300.dts

+++ b/zone0.dts

...

};

+ hvisor_virtio_device {

+ compatible = "hvisor";

+ interrupt-parent = <0x01>;

+ interrupts = <0x00 0x20 0x01>;

+ };

完成上述修改后,编译设备树文件,并将编译结果复制到 TFTP 目录。

ROOT_LINUX_DTS="zone0.dts"

TFTP_DIR="/srv/tftp"

dtc -I dts -O dtb -o zone0.dtb "${ROOT_LINUX_DTS}"

cp zone0.dtb "${TFTP_DIR}"

配置 rootfs

rootfs 直接采用烧录好的即可,不需要修改。

编译 hvisor

配置好 Rust 编译环境之后,拉取 syswonder/hvisor 仓库的 main 分支,完成编译,将编译结果复制到 TFTP 目录。

TFTP_DIR="/srv/tftp"

git clone git@github.com:syswonder/hvisor.git

cd hvisor

cargo install cargo-binutils

make BID=aarch64/sysoul-x3300

cp target/aarch64-unknown-none/debug/hvisor.bin "${TFTP_DIR}"

编译 hvisor 之前,还需要根据开发板的具体情况按需修改对应 BID 的

board.rs文件中的配置信息。可以通过 Linux 的

/proc/iomem获取内存信息,根据设备信息填写 root zone 的 memory region 信息。注意:中断控制器的地址不要与 root zone 的 memory region 重叠。

board.rs中所需的中断号可以通过设备树文件和下面的命令快速获得。DTS_FILE="zone0.dts" cat "${DTS_FILE}" \ | tr -d '\n' \ | sed 's/;/\n/g' \ | grep "interrupts =" \ | tr -d '=<>' \ | awk '{for(i=3; i<=NF; i+=3) print $(i)}' \ | while read hex; do printf "%d\n" "$((hex + 0x20))"; done \ | sort -n \ | while read dec; do printf "0x%x\n" "$dec"; done \ | tr '\n' ','

启动 hvisor + root-linux

连接串口和电源,按下 RST 重启开发板。在串口终端中观察 U-Boot 启动信息,当看到倒计时提示时,立即按下 Ctrl + C 以中断自动启动流程,进入 U-Boot 命令行。

在 U-Boot 命令行中执行命令。首先配置 IPv4 网络,以访问主机 TFTP 服务器。在确认网络配置无误之后,使用 tftp 命令依次下载 hvisor kernel device-tree,并加载到对应地址,最后通过 bootm 指令启动。

# 配置网络

setenv ipaddr 192.168.255.2

setenv netmask 255.255.255.252

setenv serverip 192.168.255.1

# 为每个文件设置正确的内存地址变量

setenv board_dtb_addr 0x00400000

setenv hvisor_addr 0x00500000

setenv kernel_addr 0x09400000

setenv root_linux_dtb_addr 0x10000000

# 从 TFTP 服务器加载每个文件到对应的内存地址

tftp ${board_dtb_addr} sysoul_x3300.dtb

tftp ${hvisor_addr} hvisor.bin

tftp ${kernel_addr} Image

tftp ${root_linux_dtb_addr} zone0.dtb

# 从 hvisor_addr 启动

bootm ${hvisor_addr} - ${board_dtb_addr}

配置好网络之后,可以通过 ping 命令测试通断。

ping ${serverip}显示结果

=> ping ${serverip} ethernet@fe1c0000 Waiting for PHY auto negotiation to complete. done Using ethernet@fe1c0000 device host 192.168.255.1 is alive

看到 root-linux 正常启动,几乎与正常基础系统无差别。

启动 GuestOS

下面以 Ubuntu-22.04 搭配 Linux 5.10 内核 为例,在 zone1 上启动 Linux。配置好 zone1 所需文件后通过 TFTP 传输到开发板上再用 hvisor-tool 启动。

root-linux 访问 TFTP 服务器需要安装 TFTP 客户端,此时通过主机 Linux 作为跳板,使得 root-linux 可以访问互联网,然后在其上通过包管理器 apt 安装 TFTP 客户端软件。

具体命令为:

开发板 root-linux 的 Debian 系统默认使用 NetworkManager 管理网络,因此我们使用

nmcli工具进行配置:# 定义网络参数 HOST_IPV4="192.168.255.1" BOARD_IPV4="192.168.255.2" NETMASK="30" DNS_SERVER="8.8.8.8" BOARD_NET_DEVICE="eth0" # 配置开发板的静态 IP 地址、子网掩码、网关和 DNS 服务器 nmcli connection modify "${BOARD_NET_DEVICE}" 802-3-ethernet.mac-address "" nmcli connection modify "${BOARD_NET_DEVICE}" connection.interface-name "${BOARD_NET_DEVICE}" nmcli connection modify "${BOARD_NET_DEVICE}" ipv4.method manual nmcli connection modify "${BOARD_NET_DEVICE}" ipv4.addresses "${BOARD_IPV4}/${NETMASK}" nmcli connection modify "${BOARD_NET_DEVICE}" ipv4.gateway "${HOST_IPV4}" nmcli connection modify "${BOARD_NET_DEVICE}" ipv4.dns "${DNS_SERVER}" nmcli connection modify "${BOARD_NET_DEVICE}" connection.autoconnect yes在主机上执行:

BOARD_IPV4="192.168.255.2" NETMASK="30" # 开启内核的 IPv4 转发功能 sudo sysctl -w net.ipv4.ip_forward=1 # 配置防火墙,允许来自开发板的流量进行转发 sudo iptables -A FORWARD -s "${BOARD_IPV4}" -j ACCEPT sudo iptables -A FORWARD -d "${BOARD_IPV4}" -j ACCEPT # 配置 NAT 规则 sudo iptables -t nat -A POSTROUTING -s "${BOARD_IPV4}/${NETMASK}" -j MASQUERADE此时开发板 root-linux 即可通过主机访问 Internet,即可执行命令安装 TFTP 客户端软件。

sudo apt update && sudo apt install tftp-hpa最后需要指出,上述所有在主机上执行的命令均为临时配置,在系统重启后会失效。若要实现永久生效,建议将这些配置写入系统的网络管理服务配置文件中或通过启动脚本固化。

编译 hvisor-tool

首先,安装交叉编译工具链。

sudo apt update && sudo apt install gcc-aarch64-linux-gnu

接下来,克隆并编译 hvisor-tool。

ROCKCHIP_LINUX_SDK_DIR="$HOME/rockchip_linux_sdk"

git clone git@github.com:syswonder/hvisor-tool.git

cd hvisor-tool

export PATH="$PATH:${ROCKCHIP_LINUX_SDK_DIR}/prebuilts/gcc/linux-x86/aarch64/gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-gnu/bin"

make all ARCH=arm64 LOG=LOG_INFO KDIR="${ROCKCHIP_LINUX_SDK_DIR}/kernel"

编译完成后,将结果放到 TFTP 目录里面。

HVISOR_TOOL_DIR="$HOME/hvisor-tool"

TFTP_DIR="/srv/tftp"

# 复制 hvisor-tool 的 driver/hvisor.ko 和 tools/hvisor

cp "${HVISOR_TOOL_DIR}/output/hvisor.ko" "${TFTP_DIR}"

cp "${HVISOR_TOOL_DIR}/output/hvisor" "${TFTP_DIR}"

准备 zone1-linux

为简化,zone1-linux 仅提供 virtio-console(提供控制台)和 virtio-vlk(提供根文件系统)。

编译 kernel

编译完成后,将结果复制到 TFTP 目录。

ROCKCHIP_LINUX_SDK_DIR="$HOME/rockchip_linux_sdk"

TFTP_DIR="/srv/tftp"

# 下载 linux 5.10 源码

git clone https://github.com/torvalds/linux -b v5.10 --depth=1

cd linux

git checkout v5.10

# 生成默认的编译配置

CROSS_COMPILE_PATH="${ROCKCHIP_LINUX_SDK_DIR}/prebuilts/gcc/linux-x86/aarch64/gcc-arm-10.3-2021.07-x86_64-aarch64-none-linux-gnu/bin"

CROSS_COMPILE_PREFIX="${CROSS_COMPILE_PATH}/aarch64-none-linux-gnu-"

make ARCH=arm64 CROSS_COMPILE=${CROSS_COMPILE_PREFIX} defconfig

# 启用 CONFIG_BLK_DEV_RAM,以启用 RAM 块设备支持

./scripts/config --enable CONFIG_BLK_DEV_RAM

# 编译

make ARCH=arm64 CROSS_COMPILE=${CROSS_COMPILE_PREFIX} Image -j$(nproc)

# 编译结果复制

cp arch/arm64/boot/Image "${TFTP_DIR}/zone1-linux.kernel"

编译 device-tree

zone1-linux 需要一个独立的设备树来描述 hvisor 为其提供的虚拟硬件环境,例如虚拟 CPU、内存布局以及 virtio 设备等。

HVISOR_DIR="$HOME/hvisor"

TFTP_DIR="/srv/tftp"

cd "${HVISOR_DIR}"

make BID=aarch64/sysoul-x3300 dtb

cp "${HVISOR_DIR}/platform/aarch64/sysoul-x3300/image/dts/zone1-linux.dtb" "${TFTP_DIR}/zone1-linux.dtb"

下载 rootfs

使用 wget 命令下载预先定义的 Ubuntu 22.04.5 的根文件系统压缩包。这是一个最小化的 Ubuntu 环境,包含了运行一个基本系统所需的核心文件。

wget https://cdimage.ubuntu.com/ubuntu-base/releases/22.04/release/ubuntu-base-22.04.5-base-arm64.tar.gz

创建一个大小为 128 MiB 的空白的磁盘镜像文件,将其格式化为 ext4 文件系统,然后将下载的根文件系统解压进去。

ZONE1_ROOTFS_IMAGE="zone1-linux-rootfs.ext4"

dd if=/dev/zero of="${ZONE1_ROOTFS_IMAGE}" bs=1M count=128 oflag=direct

mkfs.ext4 "${ZONE1_ROOTFS_IMAGE}"

mkdir -p rootfs/

sudo mount -t ext4 "${ZONE1_ROOTFS_IMAGE}" rootfs/

sudo tar -xzf ubuntu-base-22.04.5-base-arm64.tar.gz -C rootfs/

sudo umount rootfs

rm -r rootfs

完成后,将该文件链接(节省空间)到 TFTP 目录。

TFTP_DIR="/srv/tftp"

ZONE1_ROOTFS_IMAGE="zone1-linux-rootfs.img"

ABSOLUTE_IMAGE_PATH=$(realpath "${ZONE1_ROOTFS_IMAGE}")

ln "${ABSOLUTE_IMAGE_PATH}" "${TFTP_DIR}"

准备 JSON 配置文件

hvisor-tool 通过 JSON 文件来管理 zone 和 virtio 设备的配置。我们需要创建两个核心的配置文件:

zone1-linux.json:用于定义 zone 本身的资源;zone1-linux-virtio.json:用于定义其所需的 virtio 设备。

hvisor 仓库中存放了本文对应的配置文件,位于 platform/aarch64/sysoul-x3300/configs/ 目录下,使用下面的命令将其复制到 TFTP 目录下。

HVISOR_DIR="$HOME/hvisor"

TFTP_DIR="/srv/tftp"

cp "${HVISOR_DIR}/platform/aarch64/sysoul-x3300/configs/*.json" "${TFTP_DIR}"

启动 zone1-linux

在 root-linux 的 root 用户下,执行命令:

HOST_IPV4="192.168.255.1"

# 切换到 /root 目录

cd ~

# 从 TFTP 服务器上,下载 hvisor-tool 和 zone1-linux 所需内容

tftp "${HOST_IPV4}" <<EOF

get hvisor.ko

get hvisor

get zone1-linux.kernel

get zone1-linux.dtb

get zone1-linux-rootfs.ext4

get zone1-linux.json

get zone1-linux-virtio.json

quit

EOF

# 加载 hvisor.ko

insmod hvisor.ko

# 给 hvisor 添加可执行权限

chmod +x hvisor

# 启动 zone1-linux 所需的 virtio-console 和 virtio-blk

rm nohup.out

nohup ./hvisor virtio start zone1-linux-virtio.json &

# 启动 zone1-linux

./hvisor zone start zone1-linux.json

此时,执行命令

./hvisor zone list

输出为

| zone_id | cpus | name | status |

| 0 | 0, 1 | root-linux | running |

| 1 | 2, 3 | zone1-linux | running |

说明 zone1-linux 已经启动成功。

此时输入命令 cat nohup.out | grep "char device" 即可查看 zone1-linux virtio-console 对应的 pts(一般是 /dev/pts/0),此时执行命令

screen /dev/pts/0

即可连接到 zone1-linux 的 console。

提示:如何在 minicom 中分离 (detach) screen 会话

minicom和screen的默认转义键都是Ctrl+A。因此,当在minicom窗口中与screen会话交互时,需要先发送一个转义字符给minicom,再将下一个Ctrl+A传递给screen。

- 分离

screen会话的步骤:依次按下Ctrl+A,Ctrl+A,D。

基于 RK3588 的 矽慧通 X3300 快速上手 (Android 虚拟机)

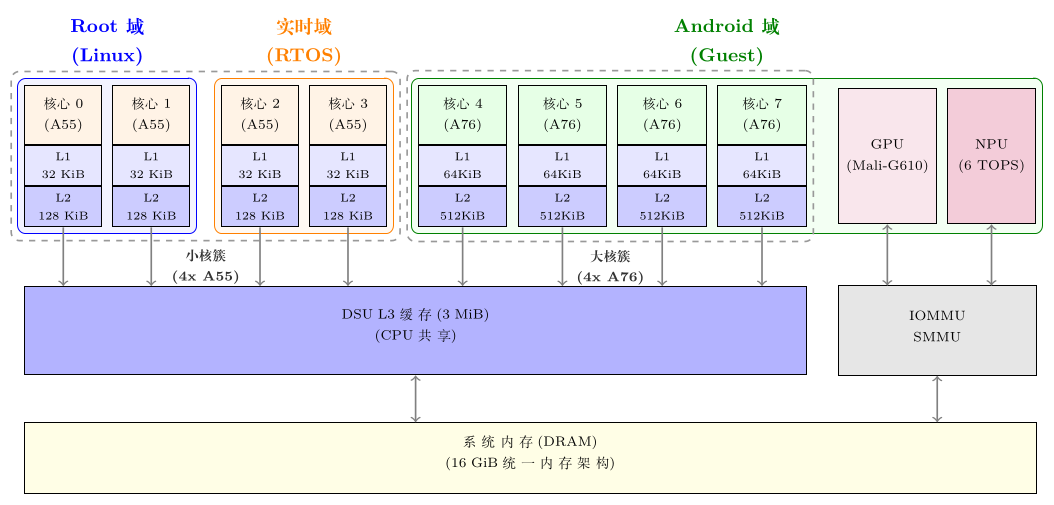

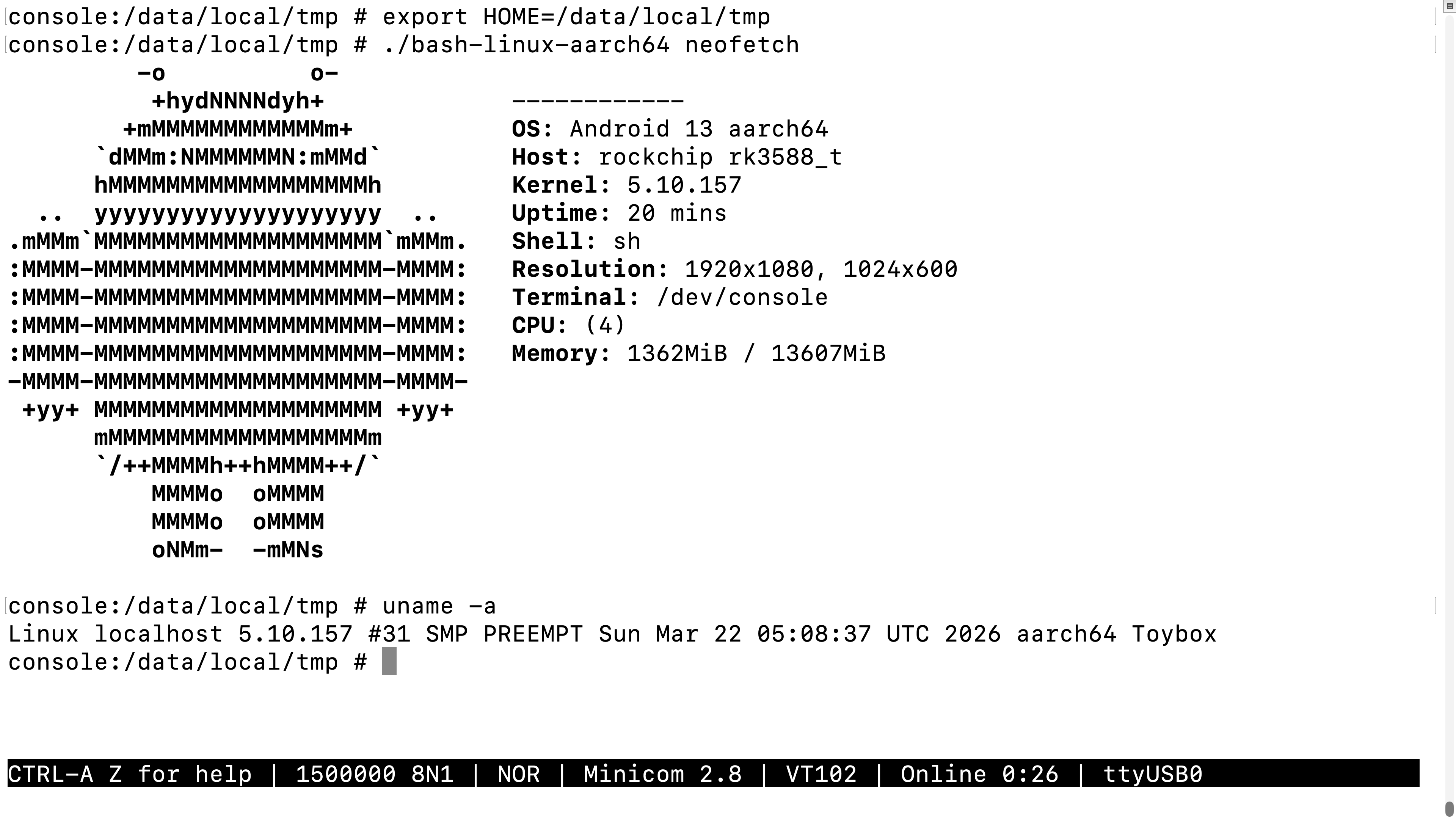

本文档旨在为开发者详细介绍在 矽慧通 X3300 开发板(亚克力版,带有 dsi 屏幕)上部署并启动 Android 虚拟机的完整流程。

操作环境基于 Ubuntu 22.04 主机。我们假定你已经参考了 基于 RK3588 的 矽慧通 X3300 快速上手 成功启动了 hvisor 以及 Root-Linux,并已经配置好主机网络与 TFTP 服务器。

由于 Android 系统包含大量图形界面相关的组件,且对硬件资源(如 GPU、NPU、多媒体、存储等)的性能要求极高,我们将采用硬件直通(Passthrough)和恒等映射(Identity Mapping)技术来满足 Android 的运行需求。

准备 Android 镜像

快捷获取预编译镜像:编译完整的 Android 和 Linux SDK 耗时较长且环境配置复杂。如果你只是想快速体验 hvisor 的 Android 虚拟化功能,可以跳过繁琐的编译和提取打包步骤。我们在百度网盘提供了已经配置好

virtio支持并编译打包好的 Root-Linux 烧录镜像(用于 SD 卡)和完整的 Androidupdate.img(用于板载 eMMC)。你可以直接下载使用:点击此处下载预编译镜像 (提取码: 394r)。

在主机上获取 Rockchip Android SDK。由于我们需要在虚拟机中启动,可以复用大部分原本供开发板裸机启动的镜像,但在编译前需要修改内核配置以支持 hvisor 的虚拟设备。

修改 Android 内核配置并编译

在 Android SDK 中,找到内核目录(kernel-5.10),修改对应的配置文件 arch/arm64/configs/rockchip_defconfig。为了支持通过 virtio 挂载的虚拟网络等设备,需要确保启用了以下配置项:

# 虚拟设备支持

CONFIG_VIRTIO_NET=y